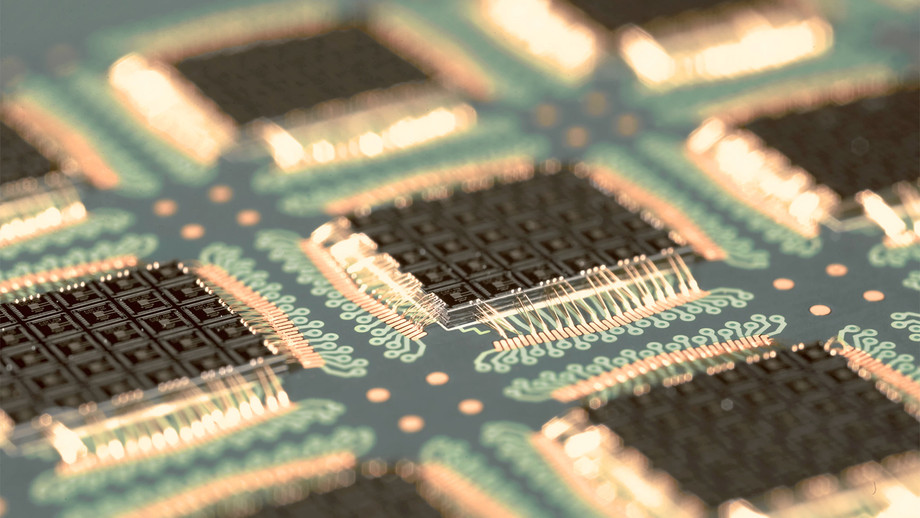

The Advanced Semiconductor Packaging Market encompasses a suite of sophisticated processes designed to protect, interconnect, and enhance semiconductor chips, enabling higher performance, reduced form factors, and improved thermal dissipation. These packaging solutions include fan-out wafer-level packaging (FOWLP), 3D IC stacking, system-in-package (SiP), and flip-chip technologies, all of which deliver compelling advantages such as lower parasitic inductance, faster signal transmission, and superior reliability under thermal stress. As end-users demand more powerful computing capabilities for applications ranging from AI and machine learning to 5G telecommunications and automotive electronics, the need for advanced packaging grows rapidly.

Manufacturers leverage novel substrates, underfills, and encapsulants to support heterogeneous integration and miniaturization, addressing Advanced Semiconductor Packaging Market challenges tied to power density and space constraints. The competitive landscape is driven by continuous research into new materials and processes that can boost yield and reduce costs, while ensuring compliance with stringent quality standards. Market research indicates that as companies vie for greater industry share through innovation, overall market size and revenue outlook remain robust.

The advanced semiconductor packaging market is estimated to be valued at USD 41.61 Bn in 2025 and is expected to reach USD 72.24 Bn by 2032, growing at a compound annual growth rate (CAGR) of 8.2% from 2025 to 2032.

Key Takeaways

Key players operating in the Advanced Semiconductor Packaging Market are:

-Advanced Micro Devices, Inc.

-Intel Corporation

-Hitachi, Ltd.

-ASE Technology Holding Co., Ltd.

-Amkor Technology

The market offers significant opportunities as electrification, artificial intelligence, and the Internet of Things (IoT) drive rapid adoption of compact, high-performance modules. With automotive OEMs integrating advanced driver-assistance systems (ADAS) and smart sensors, demand for multi-chip packages that withstand harsh environments is escalating. In consumer electronics, the push for slimmer smartphones and wearables fuels innovations in wafer-level packaging and embedded die solutions, creating lucrative market opportunities. Additionally, data center expansions and cloud computing services rely on 3D IC architectures that provide greater bandwidth and reduced latency. Emerging applications such as augmented reality (AR) and virtual reality (VR) also open new avenues for low-power, high-density packaging designs. These trends underscore a broader market forecast that anticipates growing investment in R&D and capital equipment to support advanced packaging lines. Coupled with supportive government policies in key regions, these factors are expected to bolster business growth and amplify returns for market players over the coming years.

Global expansion is a critical focus as Asia Pacific maintains a dominant industry share driven by China, Taiwan, South Korea, and Japan, which house major foundries and OSAT (outsourced semiconductor assembly and test) providers. North America continues to lead in cutting-edge market research and advanced materials development, while Europe emphasizes high-reliability packaging for aerospace and defense sectors. Market dynamics reveal that strategic partnerships, joint ventures, and capacity expansions are becoming prevalent, as global companies seek to localize production and reduce supply chain risks. Cross-border collaborations in emerging economies such as India and Southeast Asia promise to unlock untapped market segments. As regulations evolve, adherence to environmental and sustainability standards is shaping the scope of growth, compelling companies to adopt eco-friendly materials and processes. This global outlook highlights the importance of diversified manufacturing footprints and agile supply networks in capturing a larger share of the burgeoning Advanced Semiconductor Packaging Market.

Market Drivers

One of the primary drivers propelling the Advanced Semiconductor Packaging Market is the relentless demand for device miniaturization combined with enhanced performance capabilities. As electronic products converge more functionality into smaller footprints, manufacturers must overcome challenges related to heat dissipation, signal integrity, and reliability. Advanced packaging techniques such as 3D stacking and fan-out wafer-level packaging offer viable solutions by enabling vertical integration of multiple dies and improving electrical pathways. These methods reduce interconnect lengths, thus minimizing propagation delay and power consumption—critical factors in high-speed applications like 5G infrastructures and AI accelerators. Furthermore, the integration of silicon photonics and heterogeneous materials within the package broadens design possibilities, addressing emerging market requirements for higher data throughput and lower latency. This growing adoption of sophisticated packaging processes leads to economies of scale, fostering market growth. As semiconductor companies continue to invest in next-generation packaging R&D, they drive down per-unit costs and expand product portfolios, thereby unlocking new market segments and reinforcing the market’s robust growth trajectory.

PEST Analysis

Political: The global semiconductor landscape is heavily influenced by government initiatives that incentivize domestic packaging research and development through generous grants, tax credits and strategic subsidies aimed at strengthening supply chain resilience, while an evolving framework of export controls, trade restrictions and intellectual property regulations introduces market restraints that manufacturers and market drivers must carefully navigate to maintain compliance and competitive advantage.

Economic: Fluctuating raw material and substrate costs triggered by supply chain disruptions and currency volatility influence pricing strategies and profitability, while varying labor wages in major manufacturing hubs affect capital allocation decisions; disparities in regional economic growth and targeted fiscal stimulus create market opportunities yet pose cost optimization challenges across different market segments.

Social: Rising consumer demand for high-performance electronics, autonomous vehicles and wearable devices, alongside heightened environmental awareness and calls for sustainable, lead-free packaging, are prompting manufacturers to adopt circular economy practices; concurrently, shifting workforce demographics and urbanization influence talent availability and workforce training strategies in semiconductor packaging facilities, offering deep market insights for strategic planning.

Technological: The rise of heterogeneous integration techniques such as fan-out wafer-level packaging and 3D IC stacking is driving higher I/O densities, improved thermal performance and miniaturization, with through-silicon via innovations and embedded die solutions elevating functional complexity while also introducing supply constraints and cost considerations and driving strategic partnerships. Automation, artificial intelligence and machine learning applications in process monitoring, defect detection and yield optimization are reshaping production workflows, reducing cycle times and opening new business growth avenues for early adopters.

Geographical Concentration of Value

The most significant value concentration in the advanced semiconductor packaging landscape resides in the Asia Pacific region, anchored by major manufacturing hubs in China, Taiwan, South Korea and Japan. This area benefits from integrated supply chains that stretch from raw wafer fabrication through advanced fan-out and 3D packaging services, enabling efficient throughput and cost advantages. Established industry clusters in Taiwan and South Korea host leading foundries and subcontractors that serve global electronics companies, while Japan’s specialization in substrate materials and assembly equipment further cements regional dominance. North America also retains considerable relevance, driven by high-end applications, automotive electronics innovation and the presence of several key research hubs that push forward packaging process development. Europe, with its focus on automotive and industrial sectors, contributes meaningful revenues through stringent quality standards and localized assembly capabilities, though overall concentration remains secondary to Asia Pacific. Collectively, these regions illustrate where mature demand and deep investments translate into the largest pockets of value.

Fastest-Growing Region

Emerging markets across Asia Pacific continue to exhibit the fastest growth rates in advanced packaging, led by expanding semiconductor fabrication capacity in China, burgeoning electronics ecosystems in India and rising investments in Southeast Asia. Government incentives aimed at bolstering domestic chipmaking capabilities, combined with increasing outsourcing by global original equipment manufacturers seeking cost efficiencies, fuel rapid deployment of fan-out wafer-level packaging and 2.5D/3D integration facilities. India’s recent policy shifts toward production-linked incentives encourage multinational players to establish packaging lines, while Vietnam and Malaysia attract specialized service providers to support regional demand. Meanwhile, supportive frameworks in Thailand and the Philippines are nurturing a skilled workforce, enabling swift scale-up of assembly and testing operations. This convergence of policy support, talent availability and capital investment accelerates the pace at which these markets expand their advanced packaging footprint, marking them as the high-growth frontier within the global semiconductor packaging ecosystem.

‣ Get this Report in Japanese Language: 先端半導体パッケージ市場

‣ Get this Report in Korean Language: 첨단반도체패키징시장

About Author:

Ravina Pandya, Content Writer, has a strong foothold in the market research industry. She specializes in writing well-researched articles from different industries, including food and beverages, information and technology, healthcare, chemical and materials, etc. (https://www.linkedin.com/in/ravina-pandya-1a3984191)