Blog

Strona główna > Technologia pamięci Flash

Technologia pamięci Flash

Szymon Barczentewicz

Pamięci Flash są obecnie wykorzystywane w niemal każdym urządzeniu elektronicznym. Największe zalety tej technologii to wysoka wydajność, niski pobór energii, niewielkie gabaryty, masa oraz wysoka odporność na uszkodzenia [1].

Pamięć Flash została opracowana w laboratoriach Toshiby przez Dr. Fujio Masuoka na początku lat 80-tych ubiegłego wieku [1]. Pamięć Flash to połączenie technologii EPROM i EEPROM. Angielskie słowo „Flash”, rozumiane jako polski „błysk” lub „lampa błyskowa”, zostało wybrane na nazwę tej technologii z powodu możliwości wykasowania dużych bloków pamięci w jednym momencie. Taka możliwość wyraźnie odróżnia technologię Flash od technologii EEPROM, gdzie każdy bit pamięci musi być kasowany osobno.

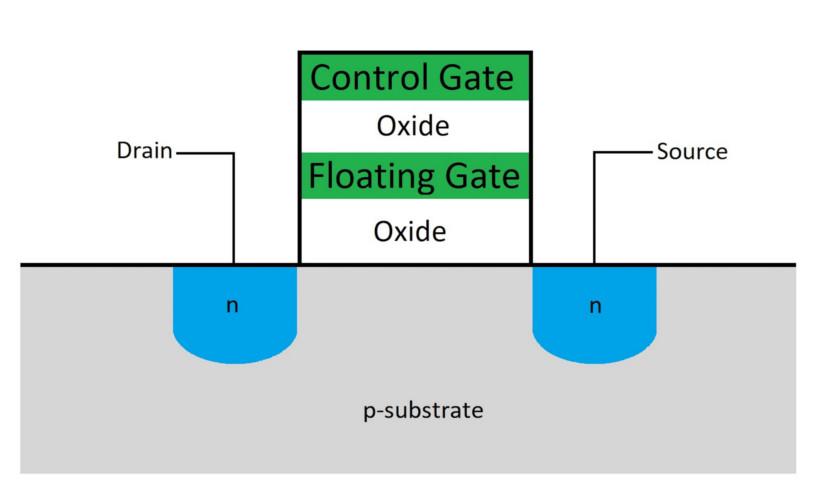

Komórka pamięci Flash składa się z jednego tranzystora z pływającą bramką. Rysunki 1 i 2 przedstawiają kolejno komórkę pamięci EPROM oraz komórkę pamięci Flash. Oba rozwiązania są do siebie bardzo podobne. Różnicę stanowi geometria układu: w szczególności bramka tlenkowa pomiędzy krzemem, a bramką pływającą jest cieńsza w przypadku technologii Flash. Również źródło i dren wykazują różnice. Dzięki tym niewielkim zmianom, w technologii EPROM uzyskano możliwość czyszczenia danych elektrycznie. Przyłożenie wysokiego napięcia o odwrotnej polaryzacji powoduje wyczyszczenie zawartości komórki. Jest to wykonywane za pomocą impulsu prądu o natężeniu bliskim 200 A. Pamięci Flash można swobodnie odczytywać i kasować tylko całymi blokami, po kilka tysięcy bitów i zmieniać stan pojedynczej komórki.

Rys. 1. Komórka pamięci EPROM [2].

Rys. 1. Komórka pamięci EPROM [2]. Rys. 2. Komórka pamięci Flash [2].

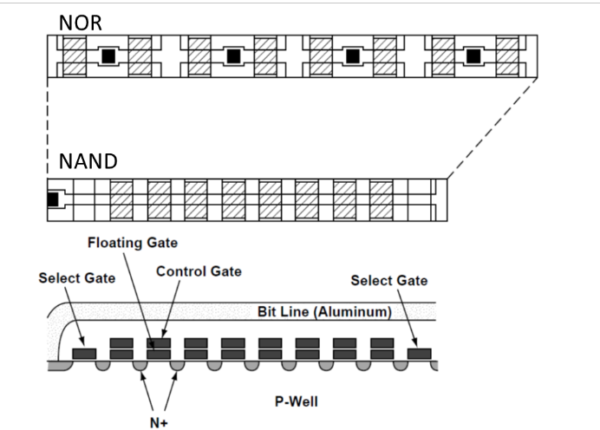

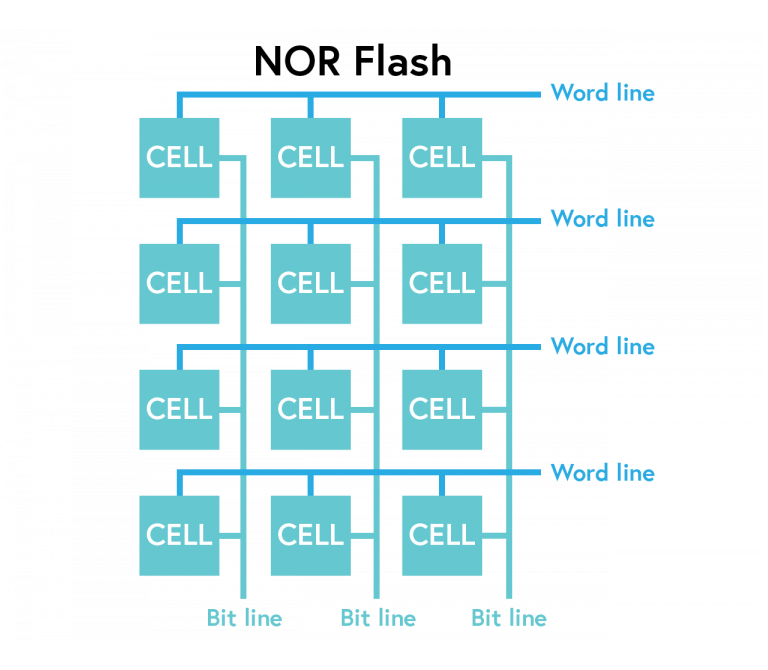

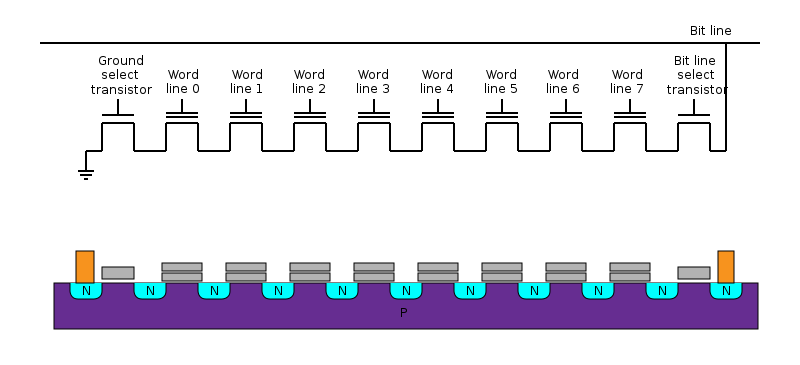

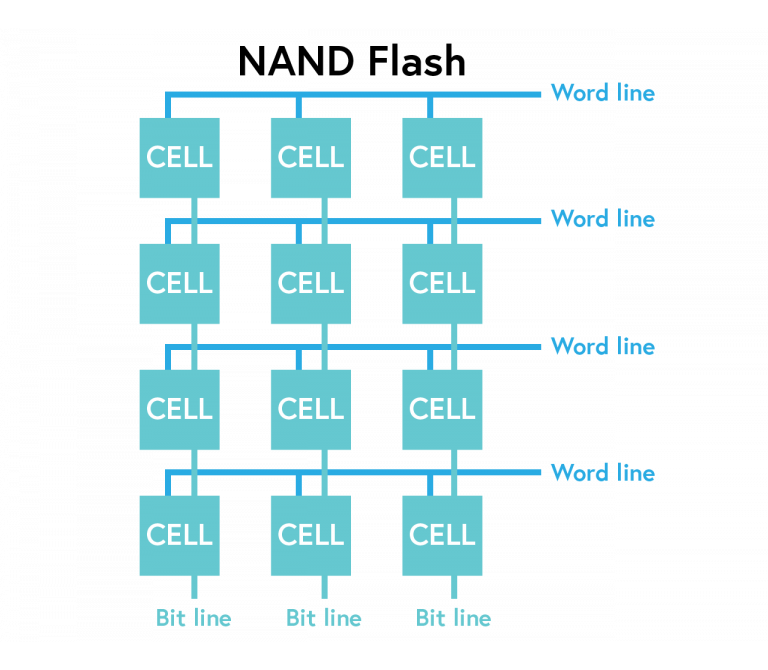

Rys. 2. Komórka pamięci Flash [2].Ze względu na rodzaj połączenia pojedynczych komórek wyróżniamy dwie odmiany pamięci Flash: NOR (połączenie równoległe) i NAND (połączenie szeregowe). W związku ze swoją budową, pamięci NAND nie mogą być odczytywane zupełnie swobodnie, a jedynie porcjami po kilka kB. Ponadto, w porównaniu do pamięci NOR, mają krótsze czasy zapisu, odczytu, większą gęstość zapisu i co za tym idzie – niższy koszt. Rysunek 3 przedstawia porównanie architektury NOR i NAND.

Rys. 3. Porównanie architektury NOR i NAND [2].

Rys. 3. Porównanie architektury NOR i NAND [2].Dyski SSD (Solid State Drive)

Popularnym rozwiązaniem wykorzystującym pamięci Flash są dyski SSD. W pierwszej kolejności dyski te ze względu na wysoką odporność na uszkodzenia wykorzystywane były głównie w komputerach przemysłowych. Obecnie są stosowane powszechnie ze względu na bardzo wysoką wydajność pracy. Rysunki 4 i 5 przedstawiają wykonane przez firmę Intel porównanie czasu pracy klasycznego dysku SSD i HDD. Można zaobserwować bardzo dużą różnicę w wydajności na korzyść dysków SSD. Dodatkowymi zaletami przemawiającymi za dyskami SDD jest niski pobór energii, bezgłośna praca czy mała waga.

Rys. 4. Czas uruchomienia Microsoft Office Proffesional 2007 [3].

Rys. 4. Czas uruchomienia Microsoft Office Proffesional 2007 [3]. Rys. 5. Czas uruchomienia World of Warcraft i Microsoft Windows Defender [3].

Rys. 5. Czas uruchomienia World of Warcraft i Microsoft Windows Defender [3].W najbliższych latach można spodziewać się sukcesywnego zwiększania się udziału na rynku nośników danych pamięci typu Flash. Dlatego bardzo ważnym i interesującym zagadnieniem będzie opracowanie technologii niszczenia danych z dysków SSD, analogicznej do tej, jaką oferują demagnetyzery dla dysków HDD.

O tym jak usunąć dane z tego typu pamięci, pisaliśmy w artykule: Czy można bezpiecznie wymazać dane z dysków SSD?

Referencje

[1] http://mimuw.edu.pl/

[2] http://smithsonianchips.si.edu/

[3] Intel.com

Zobacz także:

Programowanie FLASH

Niniejszy artykuł, przedstawiając podstawy technologii pamięci Flash, ma za zadanie wyrobić intuicję do zrozumienia istoty problemów na jakie się napotyka przy użytkowaniu scalonych układów pamięci Flash.

Zapraszamy do zapoznania się z ofertą WG Electronics w obszarze programatorów, obejmującej programatory Flash renomowanych firm:

Technologia pamięci FLASH

Nie wnikając w szczegóły technologii, historycznie programując pamięci nieulotne zapisywaliśmy bezpośrednio mapę bitową tzn. pod konkretny adres wpisywaliśmy odpowiedni bajt impulsem o zdefiniowanym czasie trwania i podwyższonym napięciu. Tak było z układami EEPROM (Electrically Erasable Programable Read-Only Memory). Zapis zmieniał poprzednią zawartość. Operacja programowania nie wymagała więc wcześniejszego kasowania zawartości, jak chociażby we wcześniejszych układach EPROM kasowanych w całości światłem UV. Współcześnie stosowane pamięci nieulotne - układy Flash, są wykonane jeszcze w innej technologii. Mają też zupełnie inną architekturę, wielkie pojemności i inny sposób programowania. Zapis wymaga wcześniejszego skasowania zawartości gdyż inne zjawiska fizyczne leżą u podstaw operacji kasowania i zapisu. Stwarzają więc zupełnie inne problemy przy ich zapisie niż EEPROM.

Spróbujmy poglądowo przedstawić istotę technologii pamięci FLASH.

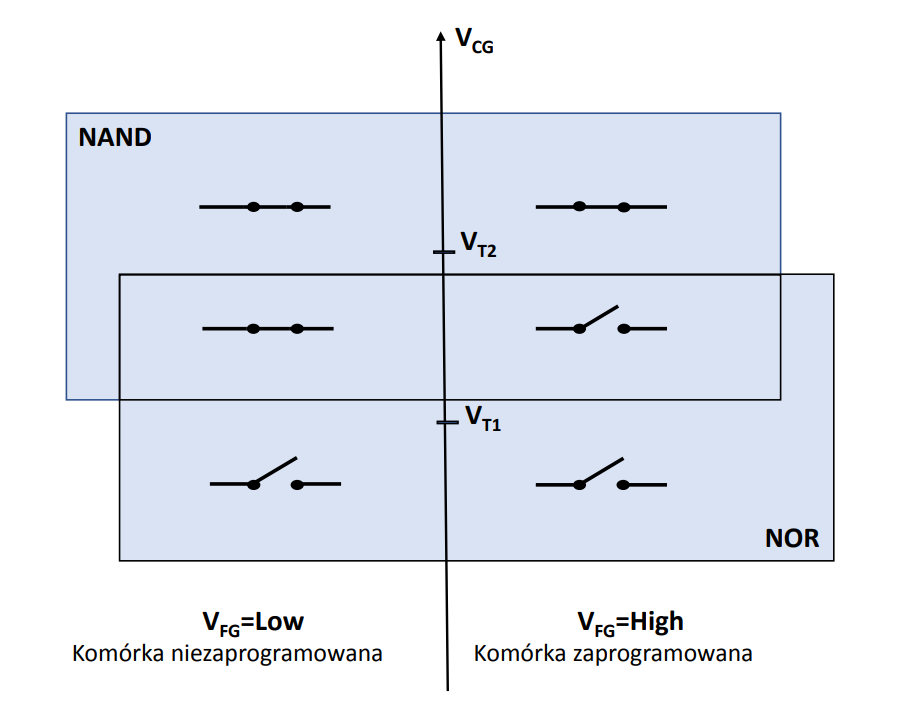

Podstawowa komórka pamięci jest zbudowana na bazie tranzystora MOSFET z dodatkową tzw. pływającą bramką FG (Floating Gate). Ta bramka „dubluje” bramkę sterującą CG (Control Gate). Pojedyncza komórka pamięci może być w uproszczeniu traktowana jako elektroniczny przełącznik, sterowany bramkami sterującą i pływającą, włączający/wyłączający przepływ prądu między źródłem i drenem. Skasowana komórka, bez ładunku w pływającej bramce, włączy się po podaniu sygnału o napięciu wyższym od pewnej wartości progowej VT1 na bramkę kontrolną i będzie przedstawiać pierwszą wartość logiczną – powiedzmy 0. Zaprogramowana komórka, z ładunkiem w pływającej bramce, ekranuje pole elektryczne bramki sterującej i podwyższa napięcie progowe załączenia do VT2 - blokuje bramkę sterującą. Komórka zaprogramowana po podaniu napięcia z zakresu (VT1,VT2) nie włączy się i będzie przedstawiać drugą wartość logiczną – powiedzmy 1. Po podaniu napięcia powyżej VT2 zarówno skasowana jak i zaprogramowana komórka włączą się.

Spójrzmy jeszcze na powyższy diagram przedstawiający stany klucza MOSFET w zależności od napięcia na bramce sterującej VCG i obecności ładunku w bramce pływającej VFG. Jak widać komórka pamięci FLASH zapewnia implementację zapamiętywania bitu cyfrowej informacji, zarówno w logice prostej jak i odwrotnej, jest logicznie funkcjonalnie pełna. Szeregowe lub równoległe połączenie tych komórek pamięci pozwala więc na realizację matryc czyli realizację układów pamięci.

Bramka pływająca jest izolowana, zachowuje ładunek po wyłączeniu zasilania. Operacja programowania polega więc na wprowadzeniu odpowiedniego ładunku do bramki pływającej w tzw. procesie tunelowania, a kasowania na usunięciu ładunku w procesie odwrotnym.

Pamięć FLASH zorganizowana jako matryca przedstawionych powyżej komórek pamięci w pojedynczej komórce typu SLC (Single-Level Cell) może pamiętać jeden bit informacji. W bardziej rozbudowanych układach, w komórkach typu MLC (Multi-Level Cell) w tym TLC (Triple-Level Cell) może pamiętać więcej bitów. Jest to osiągane przez różne poziomy ładunku w pływającej bramce FG.

Dwa główne typy pamięci Flash wzięły swoje nazwy od nazw bramek logicznych NOR i NAND co odzwierciedla sposób połączenia poszczególnych komórek pamięci w matrycy pamięci Flash. I tak…

NOR FLASH

Odpowiada równoległemu połączeniu komórek pamięci. Wtedy stan na linii odpowiadającej danemu bitowi będzie miał wartość logiczną 0, gdy co najmniej jedna z komórek pamięci dołączonych równolegle do tej linii się włączy po podaniu sygnału wyboru tej komórki pamięci po zdekodowaniu adresu słowa. Bramka pamięci NOR w stanie spoczynkowym, nie wysterowanym musi więc być zamknięta.

Pamięć NOR jest matrycą takich komórek. Jej architektura jest analogiczna do równoległych pamięci EEPROM – wybór słowa po liniowym zdekodowaniu adresu powoduje odczyt całego zapamiętanego słowa. Tak więc NOR jest preferowany w aplikacjach zintegrowanych (m.in. w mikrokontrolerach) zarówno do zapamiętywania kodu jak i danych.

W takiej strukturze aby odczytać dane, należy większość linii słów wysterować poniżej wartości VT1 niezaprogramowanej komórki. Wszystkie klucze MOSFET (zaprogramowane i niezaprogramowane) podpięte do tych linii pozostaną otwarte nie wpływając na stan linii bitów. Tylko jedną linię słowa odpowiadającą zdekodowanemu adresowi należy wysterować poniżej wartości VT2 zaprogramowanej komórki, a powyżej VT1 niezaprogramowanej komórki. Klucze MOSFET niezaprogramowanych komórek wybranego słowa ściągną wtedy linie bitów w dół. W zaprogramowanych komórkach słowa, klucze pozostaną otwarte, a linie bitów w stanie wysokim.

Ze względu na liniowe adresowanie słów pamięci NOR, analogiczne do równoległych pamięci EEPROM oraz zastosowanie jako pamięci firmware’u BIOS oczekuje się, że NOR FLASH będzie wolne od strukturalnych wad

NAND FLASH

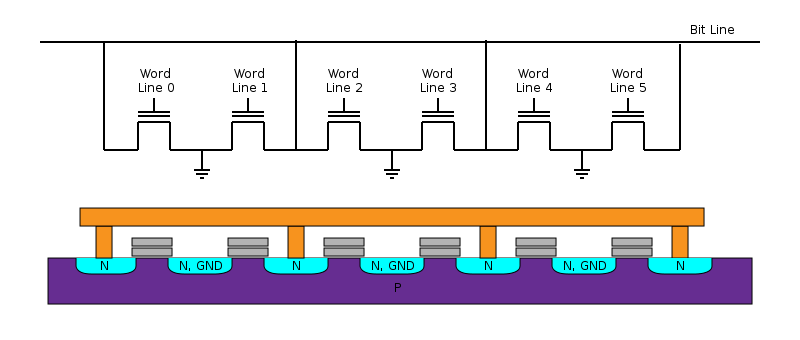

Odpowiada szeregowemu połączeniu komórek pamięci. Wtedy stan na linii odpowiadającej danemu bitowi odpowiada wartości 0, gdy wszystkie komórki szeregowo dołączone do tej linii są włączone, łącznie z wybraną zdekodowanym adresem.

Należy zwrócić uwagę, że logika układów NAND jest odwrotna w stosunku do NOR. W stanie spoczynkowym, niewysterowanym bramka musi być zamknięta.

Z logicznego punkty widzenia komórki NAND można połączyć w matrycę jak poniżej i mieć układ pamięci cyfrowej analogiczny do NOR tylko w logice odwrotnej.

Jednak współcześnie układy pamięci NAND są realizowane inaczej. Łańcuch NAND szeregowo połączonych komórek pamięci jest podłączany w strukturę NOR w miejsce pojedynczych tranzystorów MOSFET. Jest to możliwe dzięki dodatkowym kluczom w łańcuchu MOSFET, które dołączają/odłączają łańcuchy do/od linii bitów/uziemienia. W porównaniu do układów pamięci NOR architektura ta wprowadza więc dodatkowy poziom adresowania. Oprócz adresowania stron i słów dochodzi adresowanie bitów.

W takiej strukturze aby odczytać dane, najpierw wybiera się żądaną grupę (łańcuch) w sposób analogiczny do wyboru pojedynczej komórki z kluczem MOSFET w matrycy NOR. Następnie w łańcuchu większość linii słowa należy wysterować powyżej wartości VT2 zaprogramowanej komórki. Tylko jedną, wybraną linię należy wysterować powyżej wartości VT1 niezaprogramowanej komórki, a poniżej VT2 zaprogramowanej komórki. Łańcuch ściągnie wtedy linię bitu w dół, tylko wtedy gdy wybrany bit nie został zaprogramowany.

Wszystko to uzasadnia blokową i stronicową architekturę pamięci NAND. Daje intuicję dlaczego pewne operacje jak kasowanie, zapis realizowane są na pełnych blokach pamięci, a nie na pojedynczych komórkach. Taka trudniejsza do zarządzania struktura matrycy pamięci jest kosztem, za dużo większe upakowanie kluczy MOSFET w strukturach NAND czyli za osiąganie dużo większych pojemności pamięci typu NAND.

Intuicyjnie widać też, że zarządzanie adresowaniem wymaga kontrolera dostępu. We współczesnych układach NAND FLASH mniej lub bardziej zaawansowany kontroler jest wiec integralną częścią układu pamięci. Spełnia on zwykle znacznie szerszą rolę – koryguje błędy odczytu i maskuje wady fizyczne układów pamięci.

Technologia stosowana w pamięciach FLASH nie jest bowiem w 100% wolna od błędów. Stosowana jest więc suma kontrolna ECC (Error Correction Code lub Error Checking and Correction). Zastosowanie kodów korekcyjnych pozwala na detekcję wadliwego odczytu nawet występującego na wielu bitach i korekcję błędu.

I tak, napięcia potrzebne do zapisu i odczytu komórek mogą powodować niewielkie zmiany ładunku z sąsiednich komórkach, doprowadzając do wystąpienia błędów przy odczycie. Jest to efekt chwilowy, który zostaje naprawiony przy kolejnym zapisie danych do komórki. Kontroler pamięci może odświeżyć zawartość komórki, aby zapobiec utracie danych. Może to robić regularnie lub w przypadku wykrycia zbyt wielu błędów.

Inną wadą pamięci Flash jest ograniczona do około 100.000 (w przypadku komórek MLC nawet mniej) liczba cykli zapisu i kasowania. Stosowanie wysokich napięć prowadzi bowiem do stopniowego uszkadzania komórek, które z czasem są coraz trudniejsze do zaprogramowania i skasowania. Uszkodzenie warstw izolujących wokół pływającej bramki skraca również czas, przez jaki dane mogą zostać utrzymane. Pewne bloki mogą więc ulec awarii w skutek zużycia. I tak, w każdym układzie pamięci, może pojawić się pewna liczba bloków, które nie będą działały poprawnie z powodu defektów czy rozrzutu procesu produkcji. Kontroler wykrywa je na podstawie kodów korekcyjnych, gdy kolejne zapisy nie wykażą poprawy. Kontroler zapamiętuje te bloki i zmienia sposób zapisu danych w matrycy, pomijając wadliwe bloki.

Czas życia pamięci Flash można maksymalizować zapewniając, że liczba cykli zapisu i zerowania dla wszystkich bloków będzie taka sama – dzięki temu zużycie pamięci jest rozłożone równomiernie. Aby to zrealizować, kontroler pamięci musi przechowywać informacje o zużyciu bloków i wybierać najlepszy blok na zapisanie nowych danych.

Współczesne pamięci FLASH

Jak widać z powyższych rozważań, współczesne pamięci Flash wielkiej pojemności nie są pozbawione wad strukturalnych wynikających z samej technologii, procesu produkcji lub zużycia w czasie. Integralną częścią układów Flash są więc skomplikowane kontrolery pamięci zarządzające blokami pamięci, realizujące dostęp w trybie nieliniowego adresowania stronicowego i korygujące odczyt. Stopień komplikacji rośnie wraz z nowymi rozwiązaniami jak 3D, eMMC (embedded Multi Media Card), UFS (Universal Flash Storage) – a końca postępu nie widać.

Liczymy, że powyższe dalekie od naukowych rozważania pomogą w praktyce inżynierskiej gdy przyjdzie do programowania i stosowania nowoczesnych pamięci FLASH.

Zapraszamy także do zapoznania się ze stroną Programatory FLASH.

WG Electronics zapewnia w temacie programowania doradztwo i wsparcie techniczne oparte na ponad 30 letnim własnym doświadczeniu w projektowaniu, produkcji i dystrybucji programatorów oraz na doświadczeniu naszych renomowanych partnerów – wiodących światowych producentów takich urządzeń. Zapraszamy do odwiedzenia stron poświęconych naszym partnerom.

| Serwis Edukacyjny w I-LO w Tarnowie

Materiały dla uczniów liceum |

Wyjście Spis treści Wstecz Dalej

Autor artykułu: mgr Jerzy Wałaszek |

©2024 mgr Jerzy Wałaszek

|

Bity w elektronice

Cyfrowe bramki logiczne

| SPIS TREŚCI |

| Podrozdziały |

Współczesne komputery cyfrowe (istnieją również analogowe, ale tymi się tutaj nie zajmujemy) zbudowane są z milionów elementów logicznych zwanych bramkami cyfrowymi lub bramkami logicznymi (ang. digital gate). Są to elementy elektroniczne posiadające wejścia oraz wyjście danych:

Na wejścia bramki podajemy napięcia elektryczne, które mogą przyjmować dwa poziomy logiczne (dla układów TTL - Transistor-Transistor-Logic):

| poziom 0, L, F | - napięcie w przedziale 0...0,8V |

| poziom 1, H, T | - napięcie w przedziale 2...5V |

Poziomy te odpowiadają ściśle wartościom logicznym stosowanym w Algebrze Boole'a. Poziom logiczny 0 jest oznaczany często literką L od Low, czyli niski lub literką F od False, czyli fałsz. Podobnie poziom logiczny 1 jest oznaczany literką H od High, czyli wysoki lub literką T od True, czyli prawda. Wynika z tego, iż w technice cyfrowej bity są reprezentowane poziomami napięć elektrycznych (ta uwaga jest dla tych, którzy myślą, iż w komputerze jest dużo zer i jedynek - dosłownie...).

Na wyjściu bramki również dostajemy napięcie elektryczne mieszczące się w przedziale dla 0 lub 1. Napięcie to jest funkcją logiczną (np. negacją, alternatywą, koniunkcją itp.) realizowaną przez bramkę dla napięć wejściowych. W produkcji są bramki realizujące wszystkie podstawowe funkcje logiczne Algebry Boole'a. Nie będziemy się zajmować budową wewnętrzną bramki logicznej. Składa się ona z odpowiednio połączonych ze sobą elementów elektronicznych zwanych tranzystorami i opornikami. Zrozumienie ich funkcji wymaga dosyć zaawansowanych wiadomości z zakresu elektroniki elementów półprzewodnikowych, zatem darujemy sobie ten dział wiedzy, gdyż w sumie nie będzie nam on potrzebny. Potraktujemy bramkę logiczną jak czarną skrzynkę, na której wejścia podaje się odpowiednie napięcia elektryczne, a na wyjściu otrzymuje się napięcie wynikowe w funkcji napięć wejściowych - takie podejście jest zupełnie wystarczające do projektowania nawet bardzo złożonych sieci cyfrowych. Jednakże bez kilku parametrów się nie obejdzie.

Obciążalność wyjść bramki

Wyjścia bramek można łączyć z wejściami innych bramek logicznych (samych wyjść nie wolno ze sobą łączyć, ponieważ prowadzi to do zwarcia i w konsekwencji do uszkodzenia bramki) –w ten sposób powstaje sieć logiczna realizująca złożoną funkcję logiczną. Każde wejście bramki dołączone do wyjścia innej bramki pobiera z niej pewien prąd elektryczny. Wyjścia bramek mogą dostarczyć tylko określoną ilość prądu. Wynika z tego, iż do typowego wyjścia można podłączyć ograniczoną ilość wejść innych bramek. Parametr ten nosi nazwę obciążalności wyjścia bramki. Zwykle przyjmuje się go na poziomie 10 (należy sprawdzić w danych producenta) dla zwykłych bramek oraz 30 dla bramek o zwiększonej mocy wyjściowej. ( Nowoczesne układy cyfrowe oparte są na technologii CMOS i pobierają znikomy prąd na wejściu. Dzięki czemu zlikwidowano ograniczenie obciążalności do 10 wejść, teraz tych wejść może być dosłownie setki).

Obciążalności wyjściowej bramki nie należy przekraczać, gdyż może to spowodować niestabilność sieci logicznej (kłopoty z utrzymaniem odpowiedniego poziomu napięcia wyjściowego przez przeciążoną bramkę), a nawet spalenie niektórych jej elementów.

Zapamiętaj:Obciążalność wyjścia bramki logicznej określa ile wejść innych bramek można podłączyć do tego wyjścia. Dla typowych bramek obciążalność wyjścia wynosi 10 dla układów TTL. |

Czas propagacji

Poziom napięcia wyjściowego bramki jest funkcją logiczną Boole'a poziomu logicznego napięć wejściowych. Napięcie na wyjściu nie zmienia się natychmiast po zmianie poziomu napięć wejściowych, lecz po pewnym czasie - typowo po 10 ns (należy sprawdzić w danych producenta). Jest to spowodowane tym, iż tranzystory wewnątrz bramki muszą się odpowiednio poprzełączać, a to wymaga czasu.

Zapamiętaj:Czas propagacji bramki logicznej określa po jakim czasie od zmiany napięć wejściowych ustali się napięcie na wyjściu. Czas propagacji typowo wynosi 10 ns dla bramek standardowych i 3 ns dla bramek serii szybkiej. Im mniejszy czas propagacji, tym szybciej może pracować bramka. |

Czas propagacji dla sieci logicznej jest sumą czasów propagacji bramek, poprzez które przechodzi kolejno sygnał logiczny. Czasy te zawsze należy brać pod uwagę przy projektowaniu układów logicznych. W przeciwnym razie może wystąpić tzw. zjawisko hazardu.

Więcej na temat bramek logicznych znajdziesz w artykule "Układy cyfrowe".

Symbole bramek logicznych

Na schematach elektronicznych (rysunkach obrazujących sposób połączenia wejść i wyjść bramek logicznych tworzących sieć logiczną) bramki posiadają odpowiednie symbole graficzne. Istnieją odpowiednie normy, które określają jednoznacznie te symbole. My będziemy konsekwentnie stosować normę amerykańską, ponieważ jest bardzo rozpowszechniona w elektronice i bramki wyglądają zgrabnie.

Symbol bramki składa się z wejść, znaku graficznego oraz wyjść:

Wejścia będziemy oznaczać dużymi literami alfabetu A, B, C... Wyjścia będziemy oznaczać małymi literami: x, y, z. Kółeczko na wejściu lub wyjściu bramki oznacza, że dany sygnał jest zanegowany:

Symbole graficzne są następujące:

| Symbol | Funkcja |

| Tożsamość | |

|

Alternatywa |

|

Koniunkcja |

Z tych trzech symboli podstawowych oraz z symbolu negacji wejścia/wyjścia (kółeczko) buduje się symbole wszystkich bramek logicznych używanych w technice cyfrowej.

W kolejnych podrozdziałach przedstawione są podstawowe bramki logiczne wraz z ich symulacją interaktywną. W symulatorze poziomy sygnałów wejściowych określasz przez klikanie w kwadratowe przyciski. Po kliknięciu przycisk zmienia kolor:

- czarny oznacza niski stan logiczny, 0.

- czerwony oznacza wysoki stan logiczny 1.

Tymi samymi kolorami oznaczane są również linie sygnałowe. Kolor czarny oznacza stan 0 na linii, kolor czerwony oznacza stan 1. Stan wyjściowy oznaczany jest kółkiem w tych samych kolorach.

Bramka buforowa (ang. buffer gate) stosowana jest zwykle do wzmocnienia sygnału cyfrowego lub do separacji linii sygnałowych. Na wyjściu bramki otrzymujemy ten sam stan logiczny, który panuje na jej wejściu:

| A | y = A |

| 0 | 0 |

| 1 | 1 |

| Symulator |

Bramka NOT (ang. NOT gate) zwana również inwerterem wykonuje negację sygnału wejściowego. Symbol jest podobny do symbolu bufora, jednakże na wejściu lub na wyjściu umieszczone jest kółeczko, które informuje o negacji sygnału:

| A | y = NOT(A) |

| 0 | 1 |

| 1 | 0 |

| Symulator |

Bramka OR (ang. OR gate) realizuje funkcję logiczną alternatywy (lub). Bramka posiada co najmniej dwa wejścia i jedno wyjście. Stan na wyjściu jest alternatywą stanów wejściowych. Na wyjściu panuje stan logiczny 1, jeśli jedno z wejść bramki jest w stanie wysokim 1. Na wyjściu panuje stan niski 0, jeśli wszystkie wejścia bramki są w stanie niskim 0.

| A | B | y = OR(A,B) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

| Symulator |

Bramka AND (ang. AND gate) realizuje funkcję logiczną koniunkcji (i). Bramka posiada co najmniej dwa wejścia i jedno wyjście. Stan na wyjściu jest koniunkcją stanów wejściowych. Na wyjściu panuje stan logiczny 1, jeśli wszystkie wejścia bramki są w stanie wysokim 1. Na wyjściu panuje stan niski 0, jeśli przynajmniej jedno z wejść bramki jest w stanie niskim 0.

| A | B | y = AND(A,B) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| Symulator |

Bramki OR i AND są produkowane w wersjach 3, 4 i 8 wejściowych (w wydaniach specjalnych liczba wejść może być jeszcze większa). Poniżej umieściłem przykłady bramek trójwejściowych:

Bramka OR |

Bramka AND |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

Do realizacji dowolnej funkcji logicznej potrzebujemy bramki NOT oraz albo bramki AND, albo OR. Wynika to bezpośrednio z praw De Morgana oraz praw algebry Boole'a. Dla przykładu pokażemy, jak z bramek NOT i AND otrzymać funkcję OR. Najpierw zapiszmy to, co chcemy otrzymać:

| y = A ∨ B |

Zastosujemy podwójne zaprzeczenie, które nie zmienia wartości logicznej wyrażenia (podobnie jak w arytmetyce podwójny minus):

| a = ¬ ¬ a A ∨ B = ¬ ¬ ( A ∨ B ) |

Teraz wykorzystujemy prawo De Morgana: zaprzeczenie alternatywy jest koniunkcją zaprzeczeń:

| A ∨ B = ¬ ( ¬ A ∧ ¬ B ) |

Zwróć uwagę, iż wyrażenie po prawej stronie zawiera jedynie negacje i koniunkcję, a zatem da się zrealizować z bramek NOT i AND. Wyrażenie w nawiasie jest koniunkcją zaprzeczeń A i B. Wynik tej koniunkcji jest ponownie zaprzeczony.

Teraz zbudujemy odpowiednią sieć logiczną. Najpierw musimy zaprzeczyć A i B, co zrealizujemy za pomocą bramek NOT:

Wyjścia bramek NOT dają nam zanegowane sygnały A i B, które poddajemy operacji koniunkcji za pomocą bramki AND:

Mamy koniunkcję zaprzeczeń A i B. Pozostaje nam zastosować jeszcze jedną bramkę NOT, aby zaprzeczyć tę koniunkcję i otrzymać w wyniku alternatywę A i B:

Zwróć uwagę na końcowe dwie bramki: AND i NOT. Tworzą one zaprzeczoną koniunkcję (NOT AND = NAND). Powstaje z nich tzw. bramka uniwersalna NAND. Okazuje się, iż z bramek NAND można zbudować każdą sieć logiczną. Bramka NAND wewnętrznie nie składa się z dwóch oddzielnych bramek NOT i AND. Bramki NAND projektuje się, tak aby od razu otrzymać funkcję NAND bez stopni pośrednich AND i NOT, które by zwiększały czas propagacji, czyli czas ustalenia się stanu wyjścia bramki po zmianie stanu jej wejść. Z uwagi na powszechność stosowania bramka NAND posiada swój własny symbol i tabelkę stanów. Na wyjściu bramki NAND otrzymujemy stan niski 0 tylko wtedy, jeśli wszystkie jej wejścia posiadają stan wysoki 1. W przeciwnym razie na wyjściu NAND panuje stan wysoki 1:

| A | B | y = NAND(A,B) |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| Symulator |

Nasza sieć logiczna bramki OR zbudowanej z bramki NAND wygląda następująco:

Negujemy sygnały wejściowe. Negację otrzymamy podając ten sam sygnał na oba wejścia bramki NAND lub podając sygnał na jedno wejście, a na drugim utrzymując stan wysoki 1:

|

|

|

| ¬ ( A ∧ A ) = ¬ A | ¬ (1 ∧ A ) = ¬ A |

Zanegowane sygnały łączymy bramką NAND:

Czasem stosuje się do bramki NAND symbol alternatywy z zanegowanymi wejściami:

Równoważność obu symboli wynika bezpośrednio z praw De Morgana.

Bramki NAND mogą posiadać więcej niż dwa wejścia. Przemysł elektroniczny produkuje bramki NAND o 2, 3, 4, 8 i 16 wejściach. Poniżej umieściłem przykładową tabelkę stanów dla bramki 4-wejściowej NAND.

Bramka NAND |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Bramka NOR (ang. NOR gate) realizuje funkcję zaprzeczonej alternatywy (NOT OR = NOR) i jest również bramką uniwersalną, za pomocą której możemy budować dowolne sieci logiczne. W praktyce jest ona jednak mniej popularna od bramki NAND. Symbol graficzny NOR składa się z symbolu alternatywy i kółka na wyjściu symbolizującego negację. Bramka NOR przyjmuje na wyjściu stan wysoki 1 tylko wtedy, gdy wszystkie jej wejścia są w stanie niskim 0.

| A | B | y = NOR(A,B) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

| Symulator |

Dla przykładu zbudujmy z bramek NOR sieć logiczną koniunkcji dwóch sygnałów A i B. Najpierw wynik:

| y = A ∧ B |

Wykonujemy dwukrotne zaprzeczenie, które nie zmienia wartości logicznej:

| y = ¬ ¬ ( A ∧ B ) |

Wykorzystujemy prawo De Morgana: zaprzeczenie koniunkcji jest alternatywą zaprzeczeń:

| y = ¬ ( ¬ A ∨ ¬ B ) |

Otrzymaliśmy zaprzeczoną alternatywę, którą zrealizujemy za pomocą bramki NOR. Zaprzeczamy sygnały wejściowe. Można to zrobić bramkami NOR podając na oba wejścia ten sam sygnał lub podając sygnał na jedno wejście, a na drugie podając stan logiczny 0:

|

|

|

| ¬ ( A ∨ A ) = ¬ A | ¬ (A ∨ 0 ) = ¬ A |

Wyjścia łączymy bramką NOR i otrzymujemy koniunkcję sygnałów A i B:

Czasem stosuje się do bramki NOR symbol koniunkcji z zanegowanymi wejściami:

Równoważność obu symboli wynika bezpośrednio z praw De Morgana.

Bramki NOR produkowane są jako 2, 3, 4 i 8 wejściowe. Poniżej umieściłem przykładową tabelkę stanów dla bramki 4-wejściowej NOR:

Bramka NOR |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

W wielu zastosowaniach elektroniki cyfrowej wykorzystywana jest funkcja wyłącznie-lub (ang. EXclusive-OR). Funkcja EX-OR jest dwuargumentowa. Funkcja przyjmuje wartość logiczną 1 tylko wtedy, gdy dokładnie jeden z jej argumentów ma wartość 1. W przeciwnym razie funkcja ma wartość 0. Poniżej przedstawiamy symbol bramki EX-OR, tabelkę stanów oraz symulację:

| A | B | y = EX-OR(A,B) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| Symulator |

Funkcję EX-OR nazywamy również różnicą symetryczną lub sumą modulo 2. Funkcję możemy zapisać za pomocą funkcji podstawowych. Wykorzystujemy tutaj fakt, iż wartość logiczną 1 funkcja przyjmuje dla argumentów różnych:

| EX-OR(A,B) = ( A ∧ ¬ B ) ∨ ( ¬ A ∧ B ) |

Koniunkcja ( A ∧ ¬ B ) lub ( A ∧ ¬ B ) przyjmuje wartość 1, jeśli argumenty A i B posiadają przeciwne wartości logiczne. Wtedy alternatywa tych koniunkcji przyjmie wartość 1. Jeśli oba argumenty posiadają taką samą wartość logiczną, to obie koniunkcje mają wartość 0, a zatem ich alternatywa również ma wartość zero.

Spróbujmy (dla ćwiczenia) zrealizować funkcję EX-OR za pomocą bramek NAND. Wykonujemy podwójną negację:

| EX-OR(A,B) = ¬ ¬ ( ( A ∧ ¬ B ) ∨ ( ¬ A ∧ B ) ) |

Teraz wykorzystujemy prawa De Morgana, aby pozbyć się środkowej alternatywy:

| EX-OR(A,B) = ¬ ( ¬ ( A ∧ ¬ B) ∧ ¬ ( ¬ A ∧ B)) |

Zwróć uwagę, iż otrzymaliśmy tutaj same zaprzeczenia oraz funkcje zaprzeczonych koniunkcji. Wszystko da się zrealizować przy pomocy bramek NAND. Najpierw przygotowujemy sygnały A, A, B, B:

Teraz realizujemy funkcje ¬ ( A ∧ ¬ B ) oraz ¬ ( ¬ A ∧ B ):

Na koniec łączymy wyjścia tych bramek ostatnią bramką NAND i na jej wyjściu otrzymujemy funkcję EX-OR:

Produkowane przez przemysł elektroniczny bramki EX-OR nie są wewnętrznie zbudowane z żadnych bramek pośrednich. Układy te realizują wewnętrznie funkcję EX-OR, dzięki czemu są dużo szybsze w działaniu, od sieci zastępczych takich jak powyższa (to było tylko ćwiczenie). Jeśli jesteś zdolny, to spróbuj zbudować układ zastępczy bramki EX-OR z bramek NOR.

| A | B | y = EX-NOR(A,B) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| Symulator |

| Nazwa | Symbol | Funkcja | Opis |

| BUFFER | y = A | Bramka buforowa. | |

| NOT |  |

y = ¬ A | Na wyjściu jest negacja stanu wejściowego. |

| OR | y = A ∨ B | Na wyjściu jest stan 1, jeśli jedno z wejść jest w stanie 1. | |

| AND |  |

y = A ∧ B | Na wyjściu jest stan 1, jeśli wszystkie wejścia są w stanie 1. |

| NAND | y = ¬ ( A ∧ B ) | Na wyjściu jest stan 0, jeśli wszystkie wejścia są w stanie 1. | |

| NOR |   |

y = ¬ ( A ∨ B ) | Na wyjściu jest stan 1, jeśli wszystkie wejścia są w stanie 0. |

| EX-OR | y = A ⊕ B | Na wyjściu jest stan 1, jeśli oba argumenty mają różne stany logiczne. | |

| EX-NOR |  |

y = ¬ ( A ⊕ B ) | Na wyjściu jest stan 1, jeśli oba argumenty mają ten sam stan logiczny. |

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2024 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone

pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email: i-lo@eduinf.waw.pl

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.

Spis treści

ukryćPamięć flash

Zdemontowany Pamięć flash USB w 2005 r. Układ po lewej to pamięć flash. The kontroler jest po prawej stronie.

Zdemontowany Pamięć flash USB w 2005 r. Układ po lewej to pamięć flash. The kontroler jest po prawej stronie.

| Pamięć komputerowa i komputerowe przechowywanie danych typy |

|---|

|

pokazać

Generał

|

| Lotny |

|

pokazać

|

|

pokazać

Historyczny

|

| Nielotny |

|

pokazać

|

|

pokazać

|

|

pokazać

Wczesna scena NVRAM

|

|

pokazać

|

|

pokazać

|

|

pokazać

W rozwoju

|

|

pokazać

Historyczny

|

Pamięć flash jest elektroniczny nielotny pamięć komputera nośnik pamięci które można elektrycznie usunąć i przeprogramować. Dwa główne typy pamięci flash, Lampa błyskowa NOR i NAND Flash, są nazwane na cześć NOR i NAND bramy logiczne. Oba wykorzystują tę samą konstrukcję komórki, na którą składają się pływająca brama MOSFET. Różnią się na poziomie obwodu w zależności od tego, czy stan linii bitowej lub wiersza słowa jest naciągany wysoko czy nisko: w błysku NAND związek między linią bitową a wierszami słów przypomina bramę NAND; w błysku NOR przypomina bramę NOR.

Pamięć flash, rodzaj pływająca brama pamięć została wynaleziona przez Toshiba w 1980 roku i jest oparty na EEPROM technologia. Toshiba rozpoczęła marketing pamięci flash w 1987 roku.[1] EPROM musiały zostać całkowicie usunięte, zanim będą mogły zostać przepisane. Pamięć flash NAND może być jednak usuwana, zapisywana i odczytywana w blokach (lub stronach), które na ogół są znacznie mniejsze niż całe urządzenie. Pamięć flash NOR pozwala na pojedynczy słowo maszynowe do zapisania – w skasowanym miejscu – lub do samodzielnego odczytu. Urządzenie pamięci flash zazwyczaj składa się z jednej lub więcej lamp flash układy pamięci (każda z wieloma komórkami pamięci flash) wraz z osobnym kontroler pamięci flashżeton.

Typ NAND występuje głównie w karty pamięci, Dyski flash USB, dyski półprzewodnikowe (produkowane od 2009 r.), telefony z funkcjami, smartfonyoraz podobne produkty do ogólnego przechowywania i przesyłania danych. Pamięć flash NAND lub NOR jest również często używana do przechowywania danych konfiguracyjnych w produktach cyfrowych, co wcześniej było możliwe dzięki EEPROM lub zasilaniu bateryjnym statyczna pamięć RAM. Kluczową wadą pamięci flash jest to, że może wytrzymać tylko stosunkowo niewielką liczbę cykli zapisu w określonym bloku.[2)]

Flash NOR jest znany ze swoich możliwości bezpośredniego dostępu losowego, dzięki czemu jest zdolny do bezpośredniego wykonywania kodu. Jego architektura pozwala na indywidualny dostęp bajtowy, ułatwiając szybsze prędkości odczytu w porównaniu do lampy błyskowej NAND. Pamięć flash NAND działa z inną architekturą, opierając się na podejściu dostępu szeregowego. Dzięki temu NAND nadaje się do przechowywania danych o dużej gęstości, ale jest mniej wydajny w przypadku zadań losowego dostępu. Pamięć flash NAND jest często stosowana w scenariuszach, w których opłacalna pamięć masowa o dużej pojemności ma kluczowe znaczenie, takich jak dyski USB, karty pamięci i dyski półprzewodnikowe (Dyski SSD).

Główny wyróżnik polega na przypadkach użycia i strukturach wewnętrznych. Lampa błyskowa NOR jest optymalna dla aplikacji wymagających szybkiego dostępu do poszczególnych bajtów, takich jak systemy wbudowane do wykonywania programów. Z drugiej strony NAND Flash świeci w scenariuszach wymagających opłacalnej pamięci o dużej pojemności z sekwencyjnym dostępem do danych.

Pamięć flash[3] jest używany w komputery, PDA, cyfrowe odtwarzacze audio, aparaty cyfrowe, telefony komórkowe, syntezatory, gry wideo, oprzyrządowanie naukowe, robotyka przemysłowa, i elektronika medyczna. Pamięć flash ma szybki odczyt czas dostępu ale nie jest tak szybki jak statyczna pamięć RAM lub ROM. W urządzeniach przenośnych zaleca się stosowanie pamięci flash ze względu na jej odporność na wstrząsy mechaniczne, ponieważ napędy mechaniczne są bardziej podatne na uszkodzenia mechaniczne.[4]

Ponieważ cykle kasowania są powolne, duże rozmiary bloków używane do kasowania pamięci flash dają znaczną przewagę prędkości nad EEPROM bez flashowania podczas pisania dużych ilości danych. Od 2019 r. pamięć flash kosztuje znacznie mniej niż programowalna bajt EEPROM i stała się dominującym typem pamięci wszędzie tam, gdzie system wymagał znacznej ilości nielotnych półprzewodnikowe przechowywanie. EEPROM są jednak nadal używane w aplikacjach, które wymagają jedynie niewielkich ilości miejsca, jak w wykrywanie obecności szeregowej.[5][6]

Mogą korzystać pakiety pamięci flash układanie kości z vias przez krzem i kilkadziesiąt warstw komórek 3D TLC NAND (na matrycę) jednocześnie, aby osiągnąć pojemność do 1 tebibyte na opakowanie przy użyciu 16 ułożonych matryc i zintegrowanych kontroler flash jako osobna matryca w opakowaniu.[7][8][9][10]

Historia

[edytować]Tło

[edytować]Początki pamięci flash można prześledzić od rozwoju pływający MOSFET (FGMOS), znany również jako tranzystor pływający.[11][12] Oryginał MOSFET (metal – tlenek – półprzewodnikowy tranzystor polowy), znany również jako tranzystor MOS, został wynaleziony przez egipskiego inżyniera Mohamed M. Atalla i koreański inżynier Dawon Kahng o Bell Labs w 1959 r.[13] Kahng opracował odmianę MOSFET z pływającą bramą wraz z inżynierem z Tajwanu i Ameryki Simon Min Sze w Bell Labs w 1967 roku.[14] Zaproponowali, aby można go było wykorzystać jako pływającą bramę komórki pamięci do przechowywania formy programowalnej pamięć tylko do odczytu (PROM), który jest zarówno nieulotny, jak i programowalny.[14]

Wczesne typy pamięci z ruchomą bramą obejmowały EPROM (możliwy do usunięcia PROM) i EEPROM (elektrycznie kasowalny PROM) w latach siedemdziesiątych.[14] Jednak wczesna pamięć pływająca wymagała od inżynierów zbudowania komórki pamięci dla każdej z nich trochę danych, które okazały się uciążliwe,[15] wolny,[16] i drogie, ograniczające pamięć pływającą do niszowych aplikacji w latach 70., takich jak sprzęt wojskowy i najwcześniejszy eksperymentalny telefony komórkowe.[11]

Wynalazek i komercjalizacja

[edytować]Fujio Masuoka, podczas pracy dla Toshiba, zaproponował nowy typ pamięci z ruchomą bramą, który umożliwił szybkie i łatwe usunięcie całych odcinków pamięci poprzez przyłożenie napięcia do pojedynczego przewodu podłączonego do grupy komórek.[11] Doprowadziło to do wynalezienia przez Masuokę pamięci flash w Toshiba w 1980 roku.[15][17][18] Według Toshiby nazwa „flash” została zasugerowana przez kolegę Masuoki, Shōji Arizumi, ponieważ proces usuwania zawartości pamięci przypomniał mu o błysk kamery.[19] Masuoka i współpracownicy przedstawili wynalazek NOR flash w 1984 r.,[20][21] i wtedy NAND błysk na IEEE 1987 Międzynarodowe spotkanie urządzeń elektronowych (IEDM) w San Francisco.[22]

Toshiba wprowadziła na rynek pamięć flash NAND w 1987 roku.[1][14] Intel Corporation wprowadził pierwszy komercyjny układ flash typu NOR w 1988 roku.[23] Lampa błyskowa oparta na NOR ma długi czas kasowania i zapisu, ale zapewnia pełny adres i magistrale danych, pozwalając losowy dostęp do dowolnego lokalizacja pamięci. To sprawia, że jest to odpowiedni zamiennik dla starszych pamięć tylko do odczytu Układy scalone (ROM), które służą do przechowywania kodu programu, który rzadko wymaga aktualizacji, na przykład komputera BIOS lub oprogramowanie układowe z dekodery. Jego wytrzymałość może wynosić zaledwie 100 cykli kasowania dla pamięci flash na chipie,[24] do bardziej typowych 10 000 lub 100 000 cykli usuwania, do 1 000 000 cykli usuwania.[25] Lampa błyskowa oparta na NOR była podstawą wczesnych nośników wymiennych opartych na pamięci flash; CompactFlash pierwotnie był na nim oparty, chociaż późniejsze karty zostały przeniesione do tańszego NAND Flash.

Lampa błyskowa NAND skróciła czas kasowania i zapisu i wymaga mniejszej powierzchni chipa na komórkę, co pozwala na większą gęstość pamięci i niższy koszt na bit niż lampa błyskowa NOR. Jednak interfejs I / O pamięci flash NAND nie zapewnia magistrali adresu zewnętrznego o dostępie losowym. Dane należy raczej odczytywać blokowo, przy typowych rozmiarach bloków od setek do tysięcy bitów. To sprawia, że NAND flash nie nadaje się jako zamiennik programu ROM, ponieważ większość mikroprocesorów i mikrokontrolerów wymaga losowego dostępu na poziomie bajtu. Pod tym względem błysk NAND jest podobny do innych wtórnych urządzenia do przechowywania danych, takie jak dyski twarde i media optyczne, a zatem doskonale nadaje się do stosowania w urządzeniach do masowego przechowywania, takich jak karty pamięci i dyski półprzewodnikowe(SSD). Na przykład dyski SSD przechowują dane przy użyciu wielu układów pamięci flash NAND.

Pierwszym formatem wymiennej karty pamięci opartym na NAND był SmartMedia, wydany w 1995 r. Wiele innych poszło za nim, w tym MultiMediaCard, Bezpieczny cyfrowy, Pamięć Stick, i Karta obrazu xD.

Późniejsze zmiany

[edytować]Nowa generacja formatów kart pamięci, w tym RS-MMC, miniSD i microSD, charakteryzują się bardzo małymi czynnikami kształtu. Na przykład karta microSD ma powierzchnię nieco ponad 1,5 cm2), o grubości mniejszej niż 1 mm.

Flash NAND osiągnął znaczny poziom pamięci gęstość w wyniku kilku dużych technologii, które zostały skomercjalizowane od końca 2000 do początku 2010 roku.[26]

Flash NOR był najczęstszym rodzajem pamięci Flash sprzedawanej do 2005 roku, kiedy flash NAND wyprzedził NOR w sprzedaży.[27]

Komórka wielopoziomowa Technologia (MLC) przechowuje więcej niż jeden trochę w każdym komórka pamięci. NEC wykazał komórka wielopoziomowa Technologia (MLC) w 1998 r., Z 80Mb układ pamięci flash przechowujący 2 bity na komórkę.[28]STMicroelectronics wykazał również MLC w 2000 r., z 64MB Lampa błyskowa NOR układ pamięci.[29] W 2009 r. Toshiba i SanDisk wprowadzono układy flash NAND z technologią QLC przechowującą 4 bity na komórkę i utrzymującą pojemność 64Gbit.[30][31] Samsung Electronics wprowadzony komórka potrójnego poziomu Technologia (TLC) przechowuje 3 bity na komórkę i rozpoczęła masową produkcję układów NAND z technologią TLC w 2010 roku.[32]

Lampa błyskowa pułapki ładunkowej

[edytować]Lampa błyskowa pułapki ładunkowej Technologia (CTF) zastępuje pływającą bramę z polikrzemu, która jest umieszczona pomiędzy blokującym tlenkiem bramy powyżej i tunelującym tlenkiem poniżej, elektrycznie izolującą warstwą azotku krzemu; warstwa azotku krzemu uwięziła elektrony. Teoretycznie CTF jest mniej podatny na wyciek elektronów, zapewniając lepszą retencję danych.[33][34][35][36][37][38]

Ponieważ CTF zastępuje polikrzem elektrycznie izolującym azotkiem, pozwala na mniejsze komórki i wyższą wytrzymałość (niższa degradacja lub zużycie). Jednak elektrony mogą zostać uwięzione i gromadzić się w azotku, co prowadzi do degradacji. Wyciek nasila się w wysokich temperaturach, ponieważ elektrony stają się bardziej podekscytowane wzrostem temperatury. Technologia CTF nadal jednak wykorzystuje tlenek tunelowy i warstwę blokującą, które są słabymi punktami technologii, ponieważ nadal mogą zostać uszkodzone w zwykły sposób (tlenek tunelu można zdegradować z powodu bardzo wysokich pól elektrycznych i warstwy blokującej z powodu Anode Hot Hole Injection (AHHI).[39][40]

Degradacja lub zużycie tlenków jest powodem, dla którego pamięć flash ma ograniczoną wytrzymałość, a zatrzymywanie danych spada (potencjał utraty danych wzrasta) wraz ze wzrostem degradacji, ponieważ tlenki tracą swoje właściwości izolacyjne podczas degradacji. Tlenki muszą izolować się przed elektronami, aby zapobiec ich wyciekaniu, co spowodowałoby utratę danych.

W 1991 r. NEC badacze, w tym N. Kodama, K. Oyama i Hiroki Shirai opisali rodzaj pamięci flash za pomocą metody pułapki ładowania.[41] W 1998 r. Boaz Eitan z Półprzewodniki Saifun (później nabyte przez Rozpiętość) opatentowany technologia pamięci flash o nazwie NROM, która wykorzystała warstwę pułapki ładowania, aby zastąpić konwencjonalną pływająca brama stosowany w konwencjonalnych projektach pamięci flash.[42] W 2000 r. Zaawansowane mikrourządzenia Zespół badawczy (AMD) kierowany przez Richarda M. Fastow, egipski inżynier Khaled Z. Ahmed i jordański inżynier Sameer Haddad (który później dołączył do Spansion) zademonstrowali mechanizm ładowania komórek pamięci flash NOR.[43] CTF został później skomercjalizowany przez AMD i Fujitsu w 2002 r.[44] 3D V-NAND (pionowa NAND) technologia układa komórki pamięci flash NAND pionowo w układzie za pomocą technologii flash 3D ładowania pułapki (CTP). Technologia 3D V-NAND została po raz pierwszy ogłoszona przez Toshiba w 2007 roku,[45] a pierwsze urządzenie z 24 warstwami zostało po raz pierwszy wprowadzone na rynek Samsung Electronics w 2013 r.[46][47]

Technologia układów scalonych 3D

[edytować]Układ scalony 3D stosy technologii (3D IC) układ scalony (IC) układy pionowo w jednym pakiecie układów scalonych 3D.[26] Toshiba wprowadziła technologię 3D IC do pamięci flash NAND w kwietniu 2007 roku, kiedy zadebiutowali 16GB zgodny z eMMC (numer produktu THGAM0G7D8DBAI6, często w skrócie THGAM na stronach internetowych konsumentów) osadził układ pamięci flash NAND, który został wyprodukowany z ośmioma układami 2Układy flash GB NAND.[48] We wrześniu 2007 r. Hynix Semiconductor (teraz SK Hynix) wprowadził 24-warstwową technologię 3D IC z 16 Układ pamięci flash GB, który został wyprodukowany z 24 układanych układów flash NAND przy użyciu procesu łączenia płytek.[49] Toshiba zastosowała również ośmiowarstwowy układ scalony 3D dla swoich 32 Układ flash GB THGBM w 2008 roku.[50] W 2010 r. Toshiba zastosowała 16-warstwowy układ scalony 3D dla swoich 128 Układ flash GB THGBM2, który został wyprodukowany z 16 ułożonymi w stos 8 Układy GB.[51] W 2010 roku układy scalone 3D stały się szeroko stosowane komercyjnie w pamięci flash NAND w urządzenia mobilne.[26]

W 2016 r. Micron i Intel wprowadziły technologię znaną jako CMOS Under the Array / CMOS Under Array (CUA), Core over Periphery (COP), Periphery Under Cell (PUA) lub Xtacking,[52] w którym obwód sterujący pamięci flash jest umieszczony pod lub nad tablicą komórek pamięci flash. Pozwoliło to na zwiększenie liczby płaszczyzn lub sekcji, które ma układ pamięci flash, zwiększając się z 2 płaszczyzn do 4, bez zwiększania obszaru przeznaczonego na obwody sterowania lub obwodów peryferyjnych. Zwiększa to liczbę operacji IO na układ flash lub matrycę, ale wprowadza również wyzwania podczas budowania kondensatorów dla pomp ładowania używanych do zapisu w pamięci flash.[53][54][55] Niektóre matryce flash mają aż 6 samolotów.[56]

Od sierpnia 2017 r. Karty microSD o pojemności do 400 GB (400 miliardów bajtów) są dostępne.[57][58] W tym samym roku Samsung połączył układanie układów 3D IC z technologiami 3D V-NAND i TLC, aby wyprodukować 512 GB Układ pamięci flash KLUFG8R1EM z ośmioma układanymi 64-warstwowymi układami V-NAND.[8] W 2019 roku Samsung wyprodukował 1024GB układ flash, z ośmioma ułożonymi 96-warstwowymi układami V-NAND i technologią QLC.[59][60]

Zasady działania

[edytować] Komórka pamięci flash

Komórka pamięci flash

Pamięć flash przechowuje informacje w tablicy komórek pamięci wykonanych z tranzystory pływające. W komórka jednopoziomowa Urządzenia (SLC), każda komórka przechowuje tylko jeden kawałek informacji. Komórka wielopoziomowa Urządzenia (MLC), w tym komórka potrójnego poziomu Urządzenia (TLC) mogą przechowywać więcej niż jeden bit na komórkę.

Pływająca brama może być przewodząca (zazwyczaj polikrzemo w większości rodzajów pamięci flash) lub nieprzewodzące (jak w SONOS pamięć flash).[61]

MOSFET z pływającą bramą

[edytować]W pamięci flash każda komórka pamięci przypomina standard metal – tlenek – półprzewodnikowy tranzystor polowy (MOSFET) z tym wyjątkiem, że tranzystor ma dwie bramy zamiast jednej. Komórki mogą być postrzegane jako przełącznik elektryczny, w którym prąd przepływa między dwoma zaciskami (źródło i odpływ) i jest kontrolowany przez pływającą bramę (FG) i bramę sterującą (CG). CG jest podobny do bramy w innych tranzystorach MOS, ale poniżej znajduje się FG izolowany dookoła warstwą tlenku. FG jest wstawiany między CG a kanałem MOSFET. Ponieważ FG jest izolowany elektrycznie przez warstwę izolacyjną, umieszczone na nim elektrony są uwięzione. Gdy FG jest naładowane elektronami, ładunek ten ekrany . pole elektryczne z CG, zwiększając w ten sposób napięcie progowe (VT.) komórki. Oznacza to, że V.T. komórki można zmienić między nienaładowane napięcie progowe FG (VT1) i wyższy naładowane napięcie progowe FG (VT2) poprzez zmianę opłaty FG. Aby odczytać wartość z ogniwa, napięcie pośrednie (Vja) między V.T1 i V.T2 jest stosowany do CG. Jeśli kanał prowadzi w V.ja, FG musi być nieobciążony (gdyby został naładowany, nie byłoby przewodzenia, ponieważ V.ja jest mniejszy niż V.T2). Jeśli kanał nie prowadzi w V.ja, oznacza to, że FG jest naładowany. Wartość binarna komórki jest wykrywana przez ustalenie, czy prąd przepływa przez tranzystor, gdy V.ja jest potwierdzony na CG. W wielopoziomowym urządzeniu komórkowym, które przechowuje więcej niż jedno trochę na komórkę wykrywana jest ilość przepływu prądu (a nie tylko jego obecność lub brak), aby dokładniej określić poziom ładunku na FG.

Pływające bramy MOSFET są tak nazwane, ponieważ między pływającą bramą a krzemem znajduje się elektrycznie izolująca warstwa tlenku tunelu, więc brama „unosi się” nad krzemem. Tlenek utrzymuje elektrony ograniczone do pływającej bramy. Degradacja lub zużycie (i ograniczona wytrzymałość pływającej pamięci Flash) występuje z powodu wyjątkowo wysokiej pole elektryczne (10 milionów woltów na centymetr) doświadczany przez tlenek. Tak wysokie gęstości napięcia mogą z czasem zerwać wiązania atomowe w stosunkowo cienkim tlenku, stopniowo degradując jego właściwości izolacyjne elektrycznie i pozwalając na uwięzienie elektronów i swobodne przejście (wyciek) z pływającej bramy do tlenku, zwiększając prawdopodobieństwo utraty danych ponieważ elektrony (których ilość służy do reprezentowania różnych poziomów ładunku, każdy przypisany do innej kombinacji bitów w MLC Flash) zwykle znajduje się w bramce pływającej. Dlatego zatrzymywanie danych spada, a ryzyko utraty danych rośnie wraz ze wzrostem degradacji.[62][63][37][64][65]Tlenek krzemu w komórce ulega degradacji przy każdej operacji wymazywania. Degradacja zwiększa ilość ładunku ujemnego w ogniwie w czasie z powodu uwięzionych elektronów w tlenku i neguje część napięcia bramki sterującej, co z czasem powoduje również spowolnienie kasowania ogniwa, dzięki czemu zachowuje wydajność i niezawodność układu NAND , komórka musi zostać wycofana z użycia. Wytrzymałość zmniejsza się również wraz z liczbą bitów w komórce. Przy większej liczbie bitów w ogniwie liczba możliwych stanów (każdy reprezentowany przez inny poziom napięcia) w ogniwie wzrasta i jest bardziej wrażliwa na napięcia używane do programowania. Napięcia można regulować w celu skompensowania degradacji tlenku krzemu, a wraz ze wzrostem liczby bitów rośnie również liczba możliwych stanów, a zatem komórka jest mniej tolerancyjna na korekty napięć programowania,ponieważ między poziomami napięcia, które określają każdy stan w ogniwie, jest mniej miejsca.[66]

Tunelowanie Fowler – Nordheim

[edytować]Nazywa się proces przenoszenia elektronów z bramy kontrolnej do pływającej bramy Tunelowanie Fowler – Nordheimi zasadniczo zmienia charakterystykę ogniwa, zwiększając napięcie progowe MOSFET. To z kolei zmienia prąd źródłowy drenażu, który przepływa przez tranzystor dla danego napięcia bramki, które jest ostatecznie wykorzystywane do kodowania wartości binarnej. Efekt tunelowania Fowler-Nordheim jest odwracalny, więc elektrony można dodawać lub usuwać z pływającej bramy, procesy tradycyjnie znane jako pisanie i kasowanie.[67]

Wewnętrzne pompy ładujące

[edytować]Pomimo potrzeby stosunkowo wysokich napięć programowania i usuwania, praktycznie wszystkie układy flash wymagają dziś tylko jednego napięcia zasilania i wytwarzają wysokie napięcia wymagane przy użyciu układu pompy ładowania.

Ponad połowa energii zużywanej przez układ flash 1.8 V-NAND jest tracona w samej pompie ładującej. Od konwertery boost są z natury bardziej wydajne niż pompy ładowania, opracowują naukowcy niska moc Dyski SSD zaproponowały powrót do podwójnych napięć zasilania Vcc / Vpp stosowanych we wszystkich wczesnych układach flash, napędzając wysokie napięcie Vpp dla wszystkich układów flash na dysku SSD za pomocą jednego wspólnego zewnętrznego przetwornika wzmocnienia.[68][69][70][71][72][73][74][75]

W statkach kosmicznych i innych środowiskach o wysokim promieniowaniu pompa ładująca na chipie jest pierwszą częścią układu flash, która uległa awarii, chociaż pamięci flash będą nadal działać – w trybie tylko do odczytu – przy znacznie wyższych poziomach promieniowania.[76]

Lampa błyskowa NOR

[edytować] Okablowanie pamięci flash NOR i struktura na krzemie

Okablowanie pamięci flash NOR i struktura na krzemie

W pamięci flash NOR każda komórka ma jeden koniec podłączony bezpośrednio do ziemi, a drugi koniec podłączony bezpośrednio do linii bitowej. Ten układ nazywa się „NOR flash”, ponieważ działa jak Brama NOR: gdy jeden z wierszy słowa (podłączony do CG komórki) zostanie podniesiony wysoko, odpowiedni tranzystor pamięci działa, aby pociągnąć linię bitu wyjściowego na niskim poziomie. NOR flash jest nadal technologią z wyboru dla aplikacji wbudowanych wymagających dyskretnego nieulotnego urządzenia pamięci.[potrzebne cytowanie] Niskie opóźnienia odczytu charakterystyczne dla urządzeń NOR pozwalają zarówno na bezpośrednie wykonanie kodu, jak i przechowywanie danych w jednym produkcie pamięciowym.[77]

Programowanie

[edytować] Programowanie komórki pamięci NOR (ustawienie jej na logiczne 0) poprzez wstrzyknięcie gorącego elektronu

Programowanie komórki pamięci NOR (ustawienie jej na logiczne 0) poprzez wstrzyknięcie gorącego elektronu

Kasowanie komórki pamięci NOR (ustawienie jej na logiczne 1) poprzez tunelowanie kwantowe

Kasowanie komórki pamięci NOR (ustawienie jej na logiczne 1) poprzez tunelowanie kwantowe

Jednopoziomowe ogniwo flash NOR w stanie domyślnym jest logicznie równoważne binarnej wartości „1”, ponieważ prąd przepływa przez kanał przy zastosowaniu odpowiedniego napięcia do bramki sterującej, tak że napięcie linii bitowej jest obniżane. Komórkę flash NOR można zaprogramować lub ustawić na binarną wartość „0”, zgodnie z następującą procedurą:

- podwyższone napięcie (zwykle >5 V) jest stosowane do CG

- kanał jest teraz włączony, więc elektrony mogą przepływać ze źródła do odpływu (zakładając tranzystor NMOS)

- prąd drenażowy źródła jest wystarczająco wysoki, aby niektóre elektrony o wysokiej energii przeskoczyły przez warstwę izolacyjną na FG, w procesie zwanym wtrysk gorącego elektronu.

Kasowanie

[edytować]Aby usunąć ogniwo flash NOR (przywracając je do stanu „1”), duże napięcie przeciwnej biegunowości jest stosowany między CG a terminalem źródłowym, odciągając elektrony od FG przez Tunelowanie Fowler – Nordheim (Tunelowanie FN).[78] Jest to znane jako usunięcie źródła ujemnego źródła bramki. Nowsze pamięci NOR można usunąć za pomocą ujemnego wymazywania kanału bramy, co powoduje przebicie wiersza w bloku komórki pamięci NOR i studzienki P bloku komórki pamięci, aby umożliwić tunelowanie FN, usuwając blok komórki. Starsze pamięci używały wymazywania źródła, w którym do źródła przyłożono wysokie napięcie, a następnie elektrony z FG przeniesiono do źródła.[79][80] Nowoczesne układy pamięci flash NOR są podzielone na segmenty wymazywania (często nazywane blokami lub sektorami). Operację usuwania można wykonać tylko blokowo; wszystkie komórki w segmencie kasowania muszą zostać usunięte razem.[81] Programowanie komórek NOR można jednak zazwyczaj wykonywać pojedynczo lub słowo.

Okablowanie pamięci flash NAND i struktura na krzemie

Okablowanie pamięci flash NAND i struktura na krzemie

NAND Flash

[edytować]Używa również lampy błyskowej NAND tranzystory pływające, ale są połączone w sposób przypominający Brama NAND: kilka tranzystorów jest połączonych szeregowo, a linia bitowa jest naciągana nisko tylko wtedy, gdy wszystkie linie słów są naciągnięte wysoko (powyżej V tranzystorów)T.). Grupy te są następnie łączone za pomocą niektórych dodatkowych tranzystorów z tablicą linii bitów w stylu NOR w taki sam sposób, jak pojedyncze tranzystory są połączone w pamięci flash NOR.

W porównaniu z lampą błyskową NOR zastąpienie pojedynczych tranzystorów grupami połączonymi szeregowo dodaje dodatkowy poziom adresowania. Podczas gdy pamięć flash NOR może adresować pamięć według strony, a następnie słowa, pamięć flash NAND może adresować ją według strony, słowa i bitu. Adresowanie na poziomie bitowym pasuje do aplikacji szeregowych bitów (takich jak emulacja dysku twardego), które uzyskują dostęp tylko jeden bit na raz. Wykonaj na miejscu z drugiej strony aplikacje wymagają jednoczesnego dostępu do każdego słowa. Wymaga to adresowania na poziomie słowa. W każdym razie możliwe są zarówno tryby adresowania bitów, jak i słów za pomocą lampy błyskowej NOR lub NAND.

Aby odczytać dane, najpierw wybierana jest żądana grupa (w taki sam sposób, w jaki pojedynczy tranzystor jest wybierany z tablicy NOR). Następnie większość wierszy słów jest podciągnięta powyżej V.T2, podczas gdy jeden z nich jest podciągnięty do V.ja. Grupa serii przeprowadzi (i pociągnie linię bitu nisko), jeśli wybrany bit nie został zaprogramowany.

Pomimo dodatkowych tranzystorów redukcja przewodów uziemiających i linii bitowych pozwala na gęstszy układ i większą pojemność na chip. (Przewody uziemiające i linie bitów są w rzeczywistości znacznie szersze niż linie na schematach). Ponadto flash NAND zazwyczaj może zawierać pewną liczbę błędów (flash NOR, jak jest używany w przypadku BIOS Oczekuje się, że ROM będzie bezbłędny). Producenci starają się zmaksymalizować ilość użytecznego miejsca do przechowywania, zmniejszając rozmiar tranzystorów lub ogniw, jednak przemysł może tego uniknąć i osiągnąć wyższą gęstość przechowywania na matrycę, stosując 3D NAND, który układa komórki jeden na drugim.

Komórki flash NAND są odczytywane przez analizę ich odpowiedzi na różne napięcia.[64]

Pisanie i kasowanie

[edytować]Zastosowania pamięci flash NAND wtrysk tunelu do pisania i uwolnienie tunelu do usuwania. Pamięć flash NAND stanowi rdzeń wyjmowanego USB urządzenia pamięci znane jako Dyski flash USB, a także większość karta pamięci formaty i dyski półprzewodnikowe dostępne dzisiaj.

Hierarchiczna struktura lampy błyskowej NAND zaczyna się na poziomie komórki, która ustanawia ciągi, a następnie strony, bloki, płaszczyzny i ostatecznie matrycę. Ciąg to seria połączonych komórek NAND, w których źródło jednej komórki jest połączone z odpływem następnej. W zależności od technologii NAND ciąg zwykle składa się z 32 do 128 komórek NAND. Struny są zorganizowane w strony, które są następnie zorganizowane w bloki, w których każdy ciąg jest połączony z osobną linią zwaną linią bitową. Wszystkie komórki o tej samej pozycji w ciągu są połączone bramami kontrolnymi za pomocą wiersza słownego. Płaszczyzna zawiera pewną liczbę bloków połączonych tą samą linią bitową. Matryca flash składa się z jednej lub więcej płaszczyzn i obwodów peryferyjnych, które są potrzebne do wykonywania wszystkich operacji odczytu, zapisu i kasowania.

Architektura pamięci flash NAND oznacza, że dane można odczytać i zaprogramować (zapisać) na stronach, zwykle o wielkości od 4 KiB do 16 KiB, ale można je usunąć tylko na poziomie całych bloków składających się z wielu stron. Po usunięciu bloku wszystkie komórki są logicznie ustawione na 1. Dane można zaprogramować tylko w jednym przejściu do strony w skasowanym bloku. Proces programowania ustawia jedną lub więcej komórek od 1 do 0. Wszelkie komórki, które zostały ustawione na 0 przez programowanie, można zresetować do 1 tylko przez usunięcie całego bloku. Oznacza to, że zanim nowe dane będą mogły zostać zaprogramowane na stronie, która już zawiera dane, bieżąca zawartość strony oraz nowe dane muszą zostać skopiowane na nową, skasowaną stronę. Jeśli dostępna jest odpowiednia skasowana strona, dane można do niej natychmiast zapisać. Jeśli nie jest dostępna usunięta strona,blok musi zostać usunięty przed skopiowaniem danych na stronę w tym bloku. Stara strona jest następnie oznaczana jako nieprawidłowa i jest dostępna do usuwania i ponownego użycia.[82] Różni się to od systemu operacyjnego LBA zobacz na przykład, czy system operacyjny zapisuje 1100 0011 na urządzeniu pamięci flash (takim jak SSD), dane faktycznie zapisane w pamięci flash mogą wynosić 0011 1100.

Pionowy NAND

[edytować] 3D NAND kontynuuje skalowanie poza 2D.

3D NAND kontynuuje skalowanie poza 2D.

Pamięć pionowa NAND (V-NAND) lub 3D NAND układa komórki pamięci w pionie i używa flash pułapki ładowania architektura. Warstwy pionowe umożliwiają większe gęstości bitów powierzchniowych bez konieczności mniejszych pojedynczych komórek.[83] Jest również sprzedawany pod znakiem towarowym BiCS Flash, który jest znakiem towarowym Kioxia Corporation (wcześniej Toshiba Memory Corporation). 3D NAND został po raz pierwszy ogłoszony przez Toshiba w 2007 r.[45] V-NAND został po raz pierwszy komercyjnie wyprodukowany przez Samsung Electronics w 2013 r.[46][47][84][85]

Struktura

[edytować]V-NAND używa flash pułapki ładowania geometria (która została wprowadzona na rynek w 2002 r AMD i Fujitsu)[44] które przechowują opłaty w osadzie azotek krzemu film. Taki film jest bardziej odporny na wady punktowe i może być grubszy, aby pomieścić większą liczbę elektronów. V-NAND owija płaską komórkę pułapki ładunku w postać cylindryczną.[83] Począwszy od 2020 r. Pamięci flash 3D NAND firmy Micron i Intel zamiast tego używają pływających bram, jednak warstwa Micron 128 i pamięci 3D NAND używają konwencjonalnej struktury pułapki ładowania, ze względu na rozwiązanie partnerstwa między Micron i Intelem. Błysk pułapki ładowania 3D NAND jest cieńszy niż pływająca brama 3D NAND. W pływającej bramce 3D NAND komórki pamięci są całkowicie oddzielone od siebie, podczas gdy w pułapce ładowania 3D NAND pionowe grupy komórek pamięci dzielą ten sam materiał azotku krzemu.[86]

Pojedyncza komórka pamięci składa się z jednej płaskiej warstwy polikrzemu zawierającej otwór wypełniony wieloma koncentrycznymi cylindrami pionowymi. Polikrzemowa powierzchnia otworu działa jak elektroda bramkowa. Zewnętrzny cylinder z dwutlenkiem krzemu działa jak dielektryk bramkowy, zamykając cylinder z azotku krzemu, który przechowuje ładunek, z kolei zamykając cylinder z dwutlenkiem krzemu jako dielektryk tunelowy otaczający centralny pręt przewodzącego polikrzemu, który działa jak kanał przewodzący.[83]

Komórki pamięci w różnych warstwach pionowych nie zakłócają się nawzajem, ponieważ ładunki nie mogą przemieszczać się pionowo przez czynnik magazynujący azotek krzemu, a pola elektryczne związane z bramami są ściśle ograniczone w każdej warstwie. Kolekcja pionowa jest elektrycznie identyczna z grupami szeregowymi, w których skonfigurowana jest konwencjonalna pamięć flash NAND.[83] Istnieje również układanie ciągów, które buduje kilka tablic pamięci NAND 3D lub „wtyczek”[87] osobno, ale ułożone razem, aby stworzyć produkt z większą liczbą warstw 3D NAND na jednej matrycy. Często układane są dwie lub 3 tablice. Niewspółosiowość między wtyczkami jest rzędu od 30 do 10 nm.[53][88][89]

Budowa

[edytować]Wzrost grupy komórek V-NAND zaczyna się od naprzemiennego stosu przewodzących (domieszkowanych) warstw polikrzemu i izolujących warstw dwutlenku krzemu.[83]

Następnym krokiem jest utworzenie cylindrycznego otworu przez te warstwy. W praktyce 128 Gbit Układ V-NAND z 24 warstwami komórek pamięci wymaga około 2,9 miliarda takich dziur. Następnie wewnętrzna powierzchnia otworu otrzymuje wiele powłok, najpierw dwutlenek krzemu, następnie azotek krzemu, a następnie drugą warstwę dwutlenku krzemu. Na koniec otwór jest wypełniony przewodzącym (domieszkowanym) polikrzem.[83]

Wydajność

[edytować]Od 2013 r. Architektura flash V-NAND umożliwia operacje odczytu i zapisu dwa razy szybciej niż konwencjonalny NAND i może trwać do 10 razy dłużej, zużywając o 50 procent mniej energii. Oferują porównywalną fizyczną gęstość bitów przy użyciu litografii 10 nm, ale mogą być w stanie zwiększyć gęstość bitów nawet o dwa rzędy wielkości, biorąc pod uwagę użycie V-NAND do kilkuset warstw.[83] Od 2020 r. Samsung opracowuje układy V-NAND ze 160 warstwami.[90] Wraz ze wzrostem liczby warstw pojemność i wytrzymałość pamięci flash mogą zostać zwiększone.

Koszt

[edytować] Minimalny koszt bitu 3D NAND z niepionowej ściany bocznej. Górny otwór rozszerza się o więcej warstw, przeciwdziałając wzrostowi gęstości bitów.

Minimalny koszt bitu 3D NAND z niepionowej ściany bocznej. Górny otwór rozszerza się o więcej warstw, przeciwdziałając wzrostowi gęstości bitów.

Koszt płytki 3D NAND jest porównywalny ze zmniejszonym (32 nm lub mniej) płaskim błyskiem NAND.[91] Jednak przy zatrzymaniu skalowania płaskiego NAND przy 16 nm redukcja kosztu na bit może być kontynuowana przez 3D NAND, zaczynając od 16 warstw. Jednak ze względu na niepionową ścianę boczną otworu wyrytego przez warstwy; nawet niewielkie odchylenie prowadzi do minimalnego kosztu bitu, tj. minimalnej równoważnej reguły projektowej (lub maksymalnej gęstości) dla danej liczby warstw; ta minimalna liczba warstw kosztu bitu maleje dla mniejszej średnicy otworu.[92]

Ograniczenia

[edytować]Blokuj usuwanie

[edytować]Jednym z ograniczeń pamięci flash jest to, że można ją usunąć tylko blok na raz. Zasadniczo ustawia wszystkie bity w bloku na 1. Począwszy od świeżo skasowanego bloku, można zaprogramować dowolną lokalizację w tym bloku. Jednak po ustawieniu bitu na 0, tylko poprzez usunięcie całego bloku można go zmienić z powrotem na 1. Innymi słowy, pamięć flash (szczególnie pamięć flash NOR) oferuje operacje odczytu i programowania o swobodnym dostępie, ale nie oferuje dowolnych operacji przepisywania lub usuwania losowego dostępu. Lokalizację można jednak przepisać, o ile 0 bitów nowej wartości stanowi nadzbiór nadpisanych wartości. Na przykład a skubać wartość można usunąć do 1111, a następnie zapisać jako 1110. Kolejne zapisy do tego skubka mogą zmienić go na 1010, następnie 0010, a na koniec 0000. Zasadniczo wymazanie ustawia wszystkie bity na 1, a programowanie może wyczyścić tylko bity na 0.[93] Niektóre systemy plików zaprojektowane dla urządzeń flash wykorzystują tę funkcję przepisywania, na przykład Yaffs1, aby reprezentować metadane sektorowe. Inne systemy plików flash, takie jak YAFFS2, nigdy nie korzystaj z tej funkcji „przepisu” — wykonują dużo dodatkowej pracy, aby spełnić zasadę „pisz raz”.

Chociaż struktur danych w pamięci flash nie można aktualizować w całkowicie ogólny sposób, pozwala to członkom na „usunięcie” poprzez oznaczenie ich jako nieprawidłowych. Ta technika może wymagać modyfikacji komórka wielopoziomowa urządzenia, w których jedna komórka pamięci zawiera więcej niż jeden bit.

Typowe urządzenia flash, takie jak Dyski flash USB a karty pamięci zapewniają tylko interfejs na poziomie bloku, lub warstwa tłumacząca flash (FTL), który za każdym razem zapisuje w innej komórce, aby wyrównać zużycie urządzenia. Zapobiega to stopniowemu zapisywaniu w bloku; pomaga to jednak przedwcześnie zużywać urządzenie przez intensywne wzorce zapisu.

Przechowywanie danych

[edytować] 45nm NOR pamięć flash retencji danych zmieniająca się w zależności od temperatury

45nm NOR pamięć flash retencji danych zmieniająca się w zależności od temperatury

Dane przechowywane w komórkach flash są stale tracone z powodu detrapowania elektronów[potrzebna definicja]. Tempo strat rośnie wykładniczo jako temperatura bezwzględna zwiększa. Na przykład: W przypadku lampy błyskowej NOR 45 nm po 1000 godzinach strata napięcia progowego (Vt) przy 25 ° Celsjusza jest o połowę mniejsza niż przy 90 ° Celsjusza.[94]

Zużycie pamięci

[edytować]Innym ograniczeniem jest to, że pamięć flash ma skończoną liczbę cykli kasowania programu – (zwykle zapisywanych jako cykle P / E).[95][96] Technologia Micron i Sun Microsystems ogłosił układ pamięci flash SLC NAND o wartości 1 000 000 cykli P / E w dniu 17 grudnia 2008 r.[97]

Gwarantowana liczba cykli może mieć zastosowanie tylko do bloku zero (jak ma to miejsce w przypadku TSOP Urządzenia NAND) lub do wszystkich bloków (jak w NOR). Efekt ten jest łagodzony w niektórych sterownikach oprogramowania układowego lub sterownikach systemu plików poprzez zliczanie zapisów i dynamiczne mapowanie bloków w celu rozłożenia operacji zapisu między sektorami; ta technika nazywa się poziomowanie zużycia. Innym podejściem jest weryfikacja zapisu i ponowne mapowanie w sektorach zapasowych w przypadku niepowodzenia zapisu, technika zwana zły blok zarządzanie (BBM). W przypadku przenośnych urządzeń konsumenckich te techniki zarządzania zużyciem zwykle wydłużają żywotność pamięci flash poza żywotność samego urządzenia, a niektóre utraty danych mogą być dopuszczalne w tych aplikacjach. Jednak w przypadku przechowywania danych o wysokiej niezawodności nie zaleca się używania pamięci flash, która musiałaby przejść dużą liczbę cykli programowania. Ograniczenie to istnieje również w przypadku aplikacji „tylko do odczytu”, takich jak szczupli klienci i routery, które są zaprogramowane tylko raz lub najwyżej kilka razy w ciągu ich życia, z powodu czytać niepokój (patrz poniżej).

W grudniu 2012 r. Tajwańscy inżynierowie z Macronix ujawnili zamiar ogłoszenia na Międzynarodowym Spotkaniu Urządzeń Elektronowych IEEE w 2012 r., Że wymyślili, jak ulepszyć cykle odczytu / zapisu pamięci flash NAND z 10 000 do 100 milionów cykli za pomocą „samoleczenia” proces wykorzystujący układ flash z „grzewaczami pokładowymi, które mogłyby wyżalić” małe grupy komórek pamięci.[98] Wbudowane wyżarzanie termiczne miało zastąpić zwykły cykl wymazywania lokalnym procesem wysokotemperaturowym, który nie tylko usunął zmagazynowany ładunek, ale także naprawił naprężenie wywołane elektronami w układzie, dając cykle zapisu co najmniej 100 milionów.[99] Rezultatem miał być układ, który można wymazać i przepisać w kółko, nawet jeśli teoretycznie powinien się załamać. Choć przełom Macronixa mógł być obiecujący dla branży mobilnej, nie było jednak planów, aby produkt komercyjny z tą funkcją został wydany w najbliższej przyszłości.[100]

Czytaj niepokój

[edytować]Metoda zastosowana do odczytu pamięci flash NAND może powodować, że pobliskie komórki w tym samym bloku pamięci zmieniają się w czasie (zostają zaprogramowane). Jest to znane jako zaburzenie odczytu. Próg liczby odczytów znajduje się na ogół w setkach tysięcy odczytów między interwencjami usuwania. Jeśli odczyt będzie ciągły z jednej komórki, komórka ta nie zawiedzie, ale jedna z otaczających komórek będzie w kolejnym odczycie. Aby uniknąć problemu zakłócenia odczytu, kontroler flash zazwyczaj zlicza całkowitą liczbę odczytów do bloku od ostatniego skasowania. Gdy liczba przekroczy limit docelowy, dotknięty blok zostanie skopiowany do nowego bloku, usunięty, a następnie zwolniony do puli bloków. Oryginalny blok jest tak dobry jak nowy po kasowaniu. Jeśli jednak kontroler flash nie interweniuje na czas, czytać niepokój wystąpi błąd z możliwą utratą danych, jeśli błędy są zbyt liczne, aby je poprawić kod korygujący błędy.[101][102][103]

Efekty rentgenowskie

[edytować]Większość flashowych układów scalonych wchodzi tablica siatki kulkowej Pakiety (BGA), a nawet te, które nie są często montowane na płytce drukowanej obok innych pakietów BGA. Po Montaż PCB, deski z pakietami BGA są często prześwietlane, aby sprawdzić, czy kulki wykonują odpowiednie połączenia z odpowiednią podkładką, czy też BGA potrzebuje przeróbka. Te promienie rentgenowskie mogą usuwać zaprogramowane bity w układzie flash (konwertować zaprogramowane bity „0” na usunięte bity „1”). Promienie rentgenowskie nie mają wpływu na usunięte bity („1” bity).[104][105]

Niektórzy producenci produkują teraz SD odporny na promieniowanie rentgenowskie[106] i USB[107] urządzenia pamięciowe.

Dostęp na niskim poziomie

[edytować]Interfejs niskiego poziomu do układów pamięci flash różni się od interfejsu innych typów pamięci, takich jak DRAM, RZYM, i EEPROM, które obsługują zmienność bitów (zarówno od zera do jednego, jak i od jednego do zera) oraz losowy dostęp dostęp zewnętrzny autobusy adresowe.

Pamięć NOR ma zewnętrzną magistralę adresową do odczytu i programowania. W przypadku pamięci NOR odczyt i programowanie mają dostęp losowy, a odblokowywanie i kasowanie są blokowe. W przypadku pamięci NAND czytanie i programowanie odbywa się na stronie, a odblokowywanie i kasowanie odbywa się blokowo.

NOR wspomnienia

[edytować] NOR flash firmy Intel

NOR flash firmy Intel

Odczyt z pamięci flash NOR jest podobny do odczytu z pamięci o dostępie swobodnym, pod warunkiem, że adres i magistrala danych są poprawnie odwzorowane. Z tego powodu większość mikroprocesorów może używać pamięci flash NOR jako wykonać na miejscu Pamięć (XIP),[108] co oznacza, że programy przechowywane w pamięci flash NOR mogą być wykonywane bezpośrednio z pamięci flash NOR bez konieczności kopiowania do pamięci RAM. Lampa błyskowa NOR może być zaprogramowana w sposób losowy podobny do czytania. Programowanie zmienia bity z logicznego na zero. Bity, które są już zerowe, pozostają niezmienione. Wymazywanie musi odbywać się pojedynczo i resetuje wszystkie bity w skasowanym bloku z powrotem do jednego. Typowe rozmiary bloków to 64, 128 lub 256 KiB.

Złe zarządzanie blokami to stosunkowo nowa funkcja w układach NOR. W starszych urządzeniach NOR, które nie obsługują złego zarządzania blokami, oprogramowania lub sterownik urządzenia kontrolowanie układu pamięci musi być poprawne dla bloków, które się zużywają, w przeciwnym razie urządzenie przestanie działać niezawodnie.

Konkretne polecenia używane do blokowania, odblokowywania, programowania lub usuwania pamięci NOR różnią się dla każdego producenta. Aby uniknąć konieczności posiadania unikalnego oprogramowania sterownika dla każdego wyprodukowanego urządzenia, specjalnego Wspólny interfejs pamięci flash Polecenia (CFI) pozwalają urządzeniu zidentyfikować się i jego krytyczne parametry operacyjne.

Oprócz zastosowania jako pamięci ROM o dostępie swobodnym, pamięć flash NOR może być również używana jako urządzenie pamięci masowej, wykorzystując programowanie o dostępie swobodnym. Niektóre urządzenia oferują funkcję odczytu podczas zapisu, dzięki czemu kod jest kontynuowany nawet podczas działania programu lub wymazywania w tle. W przypadku sekwencyjnego zapisu danych układy flash NOR zwykle mają wolne prędkości zapisu w porównaniu z lampą błyskową NAND.

Typowy błysk NOR nie wymaga kod korygujący błąd.[109]

NAND wspomnienia

[edytować]Architektura flash NAND została wprowadzona przez Toshibę w 1989 roku.[110] Dostęp do tych wspomnień jest podobny blokuj urządzenia, takie jak dyski twarde. Każdy blok składa się z kilku stron. Strony mają zazwyczaj 512,[111] Rozmiar 2048 lub 4096 bajtów. Z każdą stroną jest kilka bajtów (zwykle 1/32 rozmiaru danych), które można wykorzystać do przechowywania kod korygujący błąd (ECC) suma kontrolna.

Typowe rozmiary bloków obejmują:

- 32 strony po 512 + 16 bajtów każda dla rozmiaru bloku (efektywnego) 16 KiB

- 64 strony po 2048 + 64 bajtów każda dla rozmiaru bloku 128 KiB[112]

- 64 strony po 4096 + 128 bajtów każda dla rozmiaru bloku 256 KiB[113]

- 128 stron po 4096 + 128 bajtów każda dla rozmiaru bloku 512 KiB.

Nowoczesna lampa błyskowa NAND może usunąć rozmiar bloku od 1 MiB do 128 MiB. Podczas gdy czytanie i programowanie odbywa się na podstawie strony, usuwanie można wykonać tylko na zasadzie blokowej.[114] Ponieważ zmiana komórki z 0 na 1 musi usunąć cały blok, a nie tylko zmodyfikować niektóre strony, więc modyfikacja danych bloku może wymagać procesu odczytu-wymazywania-zapisu, a nowe dane są faktycznie przenoszone do innego bloku. Ponadto na NVM Express SSD strefowych przestrzeni nazw, zwykle używa rozmiaru bloku flash jako rozmiaru strefy.

Urządzenia NAND wymagają również złego zarządzania blokami przez oprogramowanie sterownika urządzenia lub osobne kontroler żeton. Niektóre karty SD, na przykład, zawierają obwody kontrolera do wykonywania złego zarządzania blokami i poziomowanie zużycia. Gdy blok logiczny jest dostępny za pomocą oprogramowania wysokiego poziomu, jest on mapowany na blok fizyczny przez sterownik urządzenia lub kontroler. Wiele bloków w układzie flash można odłożyć na bok, aby przechowywać tabele mapowania w celu radzenia sobie ze złymi blokami, lub system może po prostu sprawdzić każdy blok przy włączaniu, aby utworzyć złą mapę bloków w pamięci RAM. Ogólna pojemność pamięci stopniowo maleje, ponieważ więcej bloków jest oznaczonych jako złe.

NAND polega na ECC w celu kompensacji bitów, które mogą spontanicznie ulec awarii podczas normalnej pracy urządzenia. Typowy ECC poprawi błąd jednobitowy w każdym 2048 bitach (256 bajtów) przy użyciu 22 bitów ECC lub błąd jednobitowy w każdym 4096 bitach (512 bajtów) przy użyciu 24 bitów ECC.[115] Jeśli ECC nie może poprawić błędu podczas odczytu, może nadal wykryć błąd. Podczas wykonywania operacji usuwania lub programowania urządzenie może wykryć bloki, które nie zaprogramowują lub nie usuwają, i oznaczyć je źle. Dane są następnie zapisywane w innym, dobrym bloku, a mapa złego bloku jest aktualizowana.

Kody musujące są najczęściej używanym ECC do lampy błyskowej SLC NAND. Kody Reed-Solomon i Kody BCH (Kody Bose-Chaudhuri-Hocquenghem) są powszechnie używane ECC dla lampy błyskowej MLC NAND. Niektóre układy flash MLC NAND wewnętrznie generują odpowiednie kody korekcji błędów BCH.[109]

Większość urządzeń NAND jest wysyłana z fabryki z kilkoma złymi blokami. Są one zazwyczaj oznaczane zgodnie z określoną strategią złego oznaczania bloku. Pozwalając na złe bloki, producenci osiągają znacznie wyższe wyniki plony byłoby to możliwe, gdyby wszystkie bloki musiały zostać zweryfikowane jako dobre. To znacznie zmniejsza koszty flash NAND i tylko nieznacznie zmniejsza pojemność części.

Podczas wykonywania oprogramowania z pamięci NAND, pamięć wirtualna często stosowane są strategie: najpierw musi być zawartość pamięci przywołany lub skopiowane do pamięci RAM i tam wykonane (prowadzące do wspólnej kombinacji pamięci RAM +). A jednostka zarządzania pamięcią (MMU) w systemie jest pomocny, ale można to również osiągnąć za pomocą nakładki. Z tego powodu niektóre systemy będą używać kombinacji pamięci NOR i NAND, w których mniejsza pamięć NOR jest używana jako programowa pamięć ROM, a większa pamięć NAND jest dzielona z systemem plików do użytku jako nieulotny obszar przechowywania danych.

NAND poświęca losowy dostęp i wykonanie na miejscu zalet NOR. NAND najlepiej nadaje się do systemów wymagających przechowywania danych o dużej pojemności. Oferuje wyższe gęstości, większe pojemności i niższe koszty. Ma szybsze kaucje, sekwencyjne zapisy i sekwencyjne odczyty.

Standaryzacja

[edytować]Grupa o nazwie Grupa robocza ds. Otwartego interfejsu NAND Flash (ONFI) opracował znormalizowany interfejs niskiego poziomu dla układów flash NAND. Umożliwia to interoperacyjność między zgodnymi urządzeniami NAND różnych dostawców. Specyfikacja ONFI wersja 1.0[116] został wydany 28 grudnia 2006 r. Określa:

- Standardowy interfejs fizyczny (pinout) dla NAND flash w TSOP-48, WSOP-48, LGA-52, oraz BGA-63 pakiety

- Standardowy zestaw poleceń do odczytu, zapisu i usuwania układów flash NAND

- Mechanizm samoidentyfikacji (porównywalny z wykrywanie obecności szeregowej funkcja modułów pamięci SDRAM)

Grupa ONFI jest wspierana przez głównych producentów flash NAND, w tym Hynix, Intel, Technologia Micron, i Numonyx, a także przez głównych producentów urządzeń zawierających układy flash NAND.[117]

Dwóch głównych producentów urządzeń flash, Toshiba i Samsung, zdecydowali się użyć interfejsu własnego projektu znanego jako Toggle Mode (a teraz Toggle). Ten interfejs nie jest kompatybilny pin-to-pin ze specyfikacją ONFI. W rezultacie produkt zaprojektowany dla urządzeń jednego dostawcy może nie być w stanie korzystać z urządzeń innego dostawcy.[118]